#### inst.eecs.berkeley.edu/~cs61c

## **CS61C: Machine Structures**

### **Lecture 1 – Introduction**

2004-08-30

#### **Lecturer PSOE Dan Garcia**

www.cs.berkeley.edu/~ddgarcia

**New show this Fall** ⇒ "Father of the Pride"

is the 1<sup>st</sup> attempt at prime-time 3D animation. "An Adult Comedy from makers of Shrek", premieres Tues 9pm on NBC.

www.nbc.com/nbc/Father\_of\_the\_Pride/

Garcia, Fall 2004 © UCB

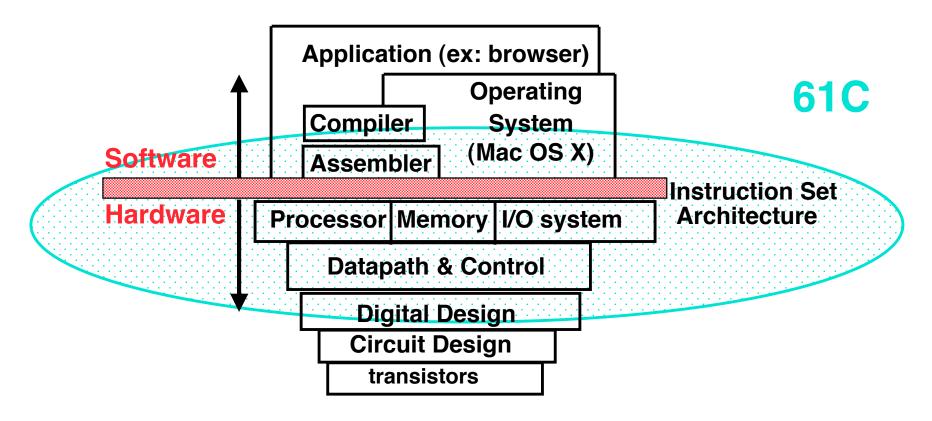

#### What are "Machine Structures"?

\* Coordination of many

levels (layers) of abstraction

## **61C Levels of Representation**

```

temp = v[k];

v(k) = v(k+1):

High Level Language

Program (e.g., C)

v(k+1) = temp;

Compiler

$t0, 0($2)

Assembly Language

$t1, 4($2)

Program (e.g., MIPS)

$t1, 0($2)

SW

$t0. 4($2

SW

Assembler

Machine Language

0000 1001 1100 0110 1010 1111 0101 1000

Program (MIPS)

1100 0110 1010 1111 0101 1000 0000 1001

0101 1000 0000 1001 1100 0110 1010 1111

Machine

Interpretation

wire [31:0] dataBus;

Hardware Architecture Description

regFile registers (databus);

(e.g., Verilog Language)

ALU ALUBlock (inA, inB, databus);

Architecture

Implementation

wire w0;

Logic Circuit Description

XOR (w0, a, b);

(Verilog Language)

AND (s, w0, a);

```

CS 61C L01 Introduction (3)

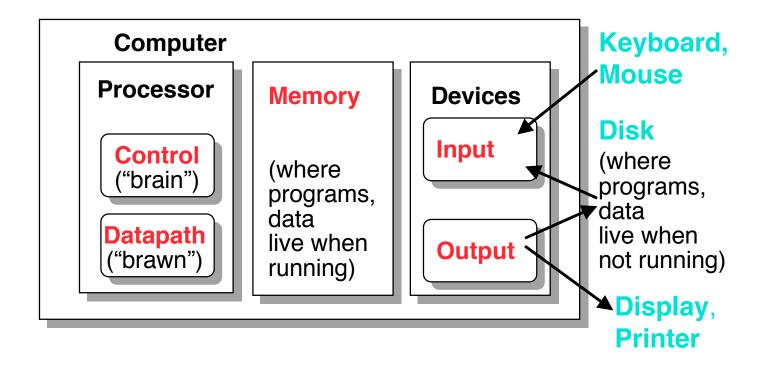

# **Anatomy: 5 components of any Computer**

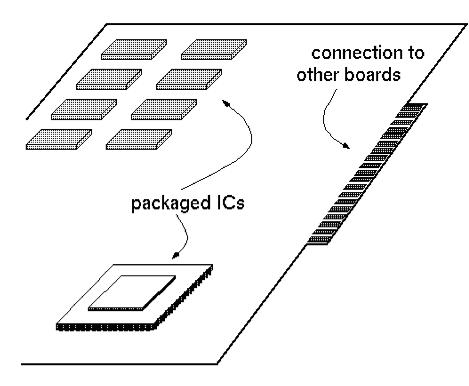

## **Overview of Physical Implementations**

The hardware out of which we make systems.

- Integrated Circuits (ICs)

- Combinational logic circuits, memory elements, analog interfaces.

- Printed Circuits (PC) boards

- substrate for ICs and interconnection, distribution of CLK, Vdd, and GND signals, heat dissipation.

- Power Supplies

- Converts line AC voltage to regulated DC low voltage levels.

- ° Chassis (rack, card case, ...)

- holds boards, power supply, provides physical interface to user or other systems.

Connectors and Cables.

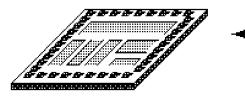

# Integrated Circuits (2003 state-of-the-art)

#### **Bare Die**

- Primarily Crystalline Silicon

- ° 1mm 25mm on a side

- ° 2003 feature size ~  $0.13\mu m = 0.13 x$   $10^{-6} m$

- 100 400M transistors

- (25 100M "logic gates")

- 3 10 conductive layers

- "CMOS" (complementary metal oxide semiconductor) - most common.

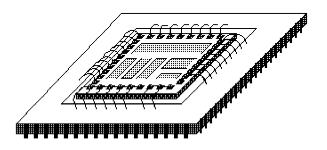

#### Chip in Package

- Package provides:

- spreading of chip-level signal paths to board-level

- heat dissipation.

- Ceramic or plastic with gold wires.

### **Printed Circuit Boards**

- ° fiberglass or ceramic

- ° 1-20 conductive layers

- ° 1-20in on a side

- ° IC packages are soldered down.

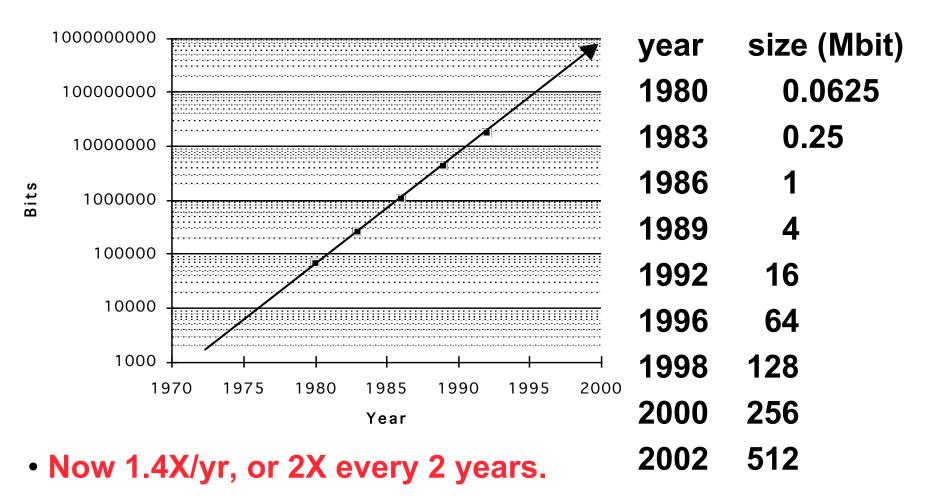

# Technology Trends: Memory Capacity (Single-Chip DRAM)

size

8000X since 1980!

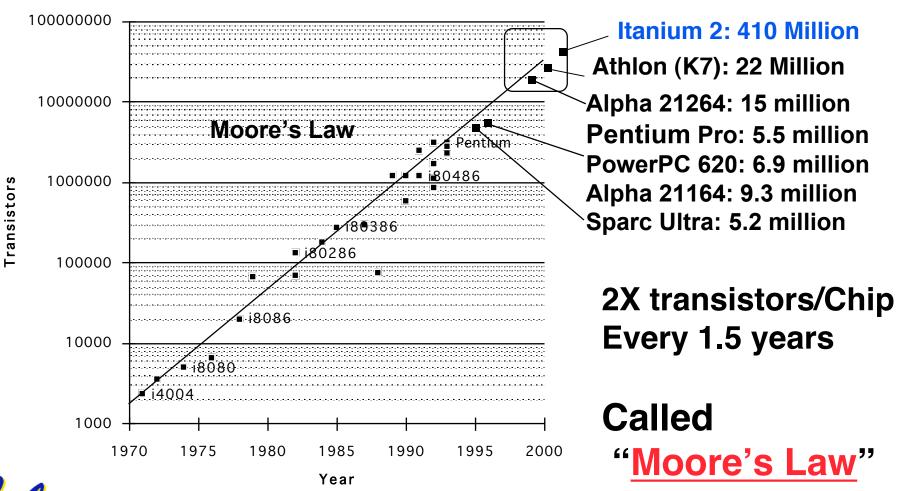

# Technology Trends: Microprocessor Complexity

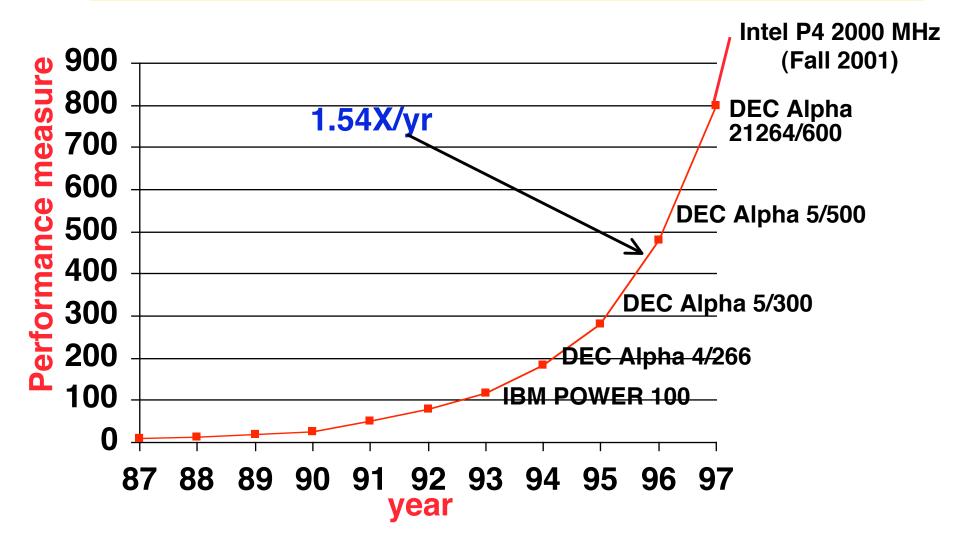

# **Technology Trends: Processor Performance**

We'll talk about processor performance later on...

# **Computer Technology - Dramatic Change!**

# ° Memory

DRAM capacity: 2x / 2 years (since '96);

64x size improvement in last decade.

#### ° Processor

Speed 2x / 1.5 years (since '85);

100X performance in last decade.

#### ° Disk

Capacity: 2x / 1 year (since '97)

250X size in last decade.

# **Computer Technology - Dramatic Change!**

°State-of-the-art PC when you graduate: (at least…)

Processor clock speed: 5000 MegaHertz

(5.0 GigaHertz)

Memory capacity: 4000 MegaBytes

(4.0 GigaBytes)

Disk capacity: 2000 GigaBytes

(2.0 TeraBytes)

New units! Mega => Giga, Giga => Tera

(Kilo, Mega, Giga, Tera,

## **Technology in the News**

#### ° BIG

- LaCie the first to offer consumer-level 1.6 Terabyte disk!

- · \$2,200

- Weighs 11 pounds!

- 5 1/4" form-factor

#### ° SMALL

- Pretec is soon offering a 12GB CompactFlash card

- Size of a silver dollar

www.lacie.com/products/product.htm?id=1012

www.engadget.com/entry/4463693158281236/

#### CS61C: So what's in it for me?

## ° Learn some of the big ideas in CS & engineering:

- 5 Classic components of a Computer

- Data can be anything (integers, floating point, characters): a program determines what it is

- Stored program concept: instructions just data

- Principle of Locality, exploited via a memory hierarchy (cache)

- Greater performance by exploiting parallelism

- Principle of abstraction, used to build systems as layers

- Compilation v. interpretation thru system layers

- Principles/Pitfalls of Performance Measurement

### Others Skills learned in 61C

# °Learning C

- If you know one, you should be able to learn another programming language largely on your own

- Given that you know C++ or Java, should be easy to pick up their ancestor, C

# Assembly Language Programming

This is a skill you will pick up, as a side effect of understanding the Big Ideas

# Hardware design

- We think of hardware at the abstract level, with only a little bit of physical logic to give things perspective

- CS 150, 152 teach this

### **Course Lecture Outline**

- Number representations

- ° C-Language (basics + pointers)

- ° Storage management

- Assembly Programming

- ° Floating Point

- ° make-ing an Executable

- ° Caches

- Virtual Memory

- Logic Design

- Introduction to Verilog (HDL)

- ° CPU organization

- ° Pipelining

- ° Performance

- ° I/O Interrupts

- ° Disks, Networks

- Advanced Topics

#### **Texts**

Required: Computer Organization and Design: The Hardware/Software Interface, Third Edition, Patterson and Hennessy (COD). The second edition is far inferior, and is not suggested.

- °Required: *The C Programming Language*, Kernighan and Ritchie (K&R), 2nd edition

- ° Reading assignments on web page

## **Tried-and-True Technique: Peer Instruction**

- Increase real-time learning in lecture, test understanding of concepts vs. details

- °As complete a "segment" ask multiple choice question

- 1-2 minutes to decide yourself

- 3 minutes in pairs/triples to reach consensus. Teach others!

- 5-7 minute discussion of answers, questions, clarifications

- Buy PRS transmitters from ASUC student store or others

#### **Peer Instruction**

- Read textbook, review lectures (new or old) before class

- Reduces examples have to do in class

- Get more from lecture (also good advice)

- °Fill out 3-question Web Form on reading (deadline 9am before lecture)

- Graded for effort, not correctness

- Count for "effort" points

## **Weekly Schedule**

### There IS discussion and lab this week...

## Homeworks, Labs and Projects

- Lab exercises (every wk; due in that lab session unless extension given by TA)

- Objective of the image of th

- °Projects (every 2 to 3 weeks)

- °All exercises, reading, homeworks, projects on course web page

- °We will DROP your lowest HW, Lab!

- Only one {HW, Project, Midterm} / week

#### 2 Course Exams + 2 Faux Exams

- Midterm: Early 8th week, room TBA

- Give 2 hours for 1 hour exam

- Open Book / Notes

- Review session TBA

- 2 Faux Midterms for feedback

- Honor system: take @ home, tell us your score for each question, we check off.

- A bad score won't hurt. Not doing it will.

- Final: Sat 2004-05-14 @ 12:30-3:30pm

- You can *clobber* your midterm grade!

- (students last semester LOVED this...)

# Your final grade

## ° Grading (could change before 1st midterm)

- 15pts = 5% Labs

- 30pts = 10% Homework

- 45pts = 15% Projects

- 75pts = 25% Midterm\* [can be clobbered by Final]

- 135pts = 45% Final

- + Extra credit for EPA. What's EPA?

#### Grade distributions

- Similar to CS61B, in the absolute scale.

- Perfect score is 300 points. 10-20-10 for A+, A, A-

- Similar for Bs and Cs (40 pts per letter-grade)

- ... C+, C, C-, D, F (No D+ or D- distinction)

- Differs: No F will be given if all-but-one {hw, lab}, all projects submitted and all exams taken

We'll "ooch" grades up but never down

#### **Extra Credit: EPA!**

#### Effort

Attending Dan's and TA's office hours, completing all assignments, turning in HW0, doing reading quizzes

## Participation

- Attending lecture and voting using the PRS system

- Asking great questions in discussion and lecture and making it more interactive

#### Altruism

Helping others in lab or on the newsgroup

EPA! extra credit points have the potential to bump students up to the next grade level! (but actual EPA! scores are internal)

## **Course Problems...Cheating**

- ° What is cheating?

- Studying together in groups is encouraged.

- Turned-in work must be <u>completely</u> your own.

- Common examples of cheating: running out of time on a assignment and then pick up output, take homework from box and copy, person asks to borrow solution "just to take a look", copying an exam question, ...

- Both "giver" and "receiver" are equally culpable

- Cheating on homeworks: negative points for that assignment (e.g., if it's worth 10 pts, you get -10)

- ° Cheating on projects / exams; At least, negative points for that project / exam. In most cases, F in the course.

- Every offense will be referred to the Office of Student Judicial Affairs.

www.eecs.berkeley.edu/Policies/acad.dis.shtml

#### **Enrollment**

°We will not be enforcing the CS61B prerequisite this semester.

## **Teaching Assistants**

- Paul Burstein

- °José María González [co-head TA]

- °Andy Carle [co-head TA]

- Output

Andrew Schultz

- °Slav Petrov

- Steven Kusalo

# **Student Learning Center (SLC)**

- °Cesar Chavez Center (on Lower Sproul)

- The SLC will offer directed study groups for students CS 61C. This will be our first semester supporting CS 61C with a study group, but based on our pilot offering of tutoring in Spring 2004, we believe that it will be well received. We will also offer Drop-in tutoring support for about 20 hours each week. Most of these hours will be conducted by paid tutorial staff, but these will also be supplemented by students who are receiving academic credit for tutoring.

# **Summary**

- Continued rapid improvement in computing

- 2X every 2.0 years in memory size; every 1.5 years in processor speed; every 1.0 year in disk capacity;

- Moore's Law enables processor (2X transistors/chip ~1.5 yrs)

- °5 classic components of all computers Control Datapath Memory Input Output