| 5   | Decoding                                                              | g Exan                                            | nple (2                                            | 2/7)                                                |                                           |                   |

|-----|-----------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|-------------------------------------------|-------------------|

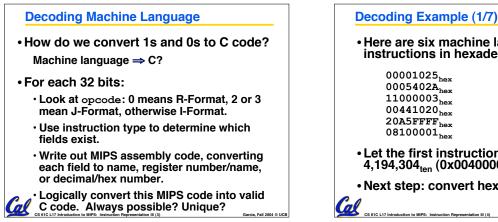

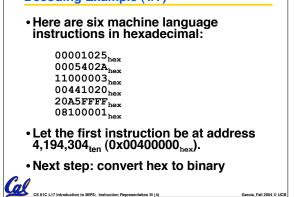

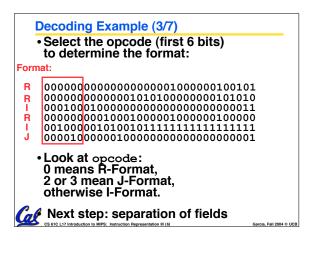

| •   | The six i<br>binary:                                                  | machin                                            | e langı                                            | lage ins                                            | structio                                  | ns in             |

| •   | 00000000<br>00010001<br>00000000<br>00100000<br>000010000<br>Next ste | 0000001<br>000000<br>010001<br>0101001<br>0000100 | 0101000<br>0000000<br>0000010<br>011111<br>0000000 | 0000001<br>0000000<br>0000001<br>1111111<br>0000000 | 01010<br>00011<br>00000<br>11111<br>00001 | at                |

| R   | 0                                                                     | rs                                                | rt                                                 | rd                                                  | shamt                                     | funct             |

| 1   | 1, 4-31                                                               | rs                                                | rt                                                 | ir                                                  | nmedia                                    | te                |

| J   | 2 or 3                                                                |                                                   | targe                                              | t add                                               | ress                                      |                   |

| Cal | CS 61C L17 Introductic                                                |                                                   |                                                    |                                                     |                                           | Garcia, Fall 2004 |

## **Decoding Example (4/7)**

· Fields separated based on format/opcode: Format:

| R | 0 | 0 | 0 | 2      | 0  | 37 |

|---|---|---|---|--------|----|----|

| R | 0 | 0 | 5 | 8      | 0  | 42 |

| 1 | 4 | 8 | 0 |        | +3 |    |

| R | 0 | 2 | 4 | 2      | 0  | 32 |

| 1 | 8 | 5 | 5 |        | -1 |    |

| J | 2 |   | 1 | ,048,5 | 77 |    |

Next step: translate ("disassemble") to MIPS assembly instructions CS 61C L17 Introduction to MIPS: Instruction Representation III (7)

Garcia, Fall 2004 © UCB

| Decoding Exam                                                                     | nple (5/7)                           | )                                                                                |                         |

|-----------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|-------------------------|

| MIPS Assemb                                                                       | ly (Part                             | 1):                                                                              |                         |

| Address:                                                                          | Asser                                | nbly instructi                                                                   | ons:                    |

| 0x00400000<br>0x00400004<br>0x00400008<br>0x0040000c<br>0x004000010<br>0x00400014 | or<br>slt<br>beq<br>add<br>addi<br>j | \$2,\$0,\$0<br>\$8,\$0,\$5<br>\$8,\$0,3<br>\$2,\$2,\$4<br>\$5,\$5,-1<br>0*100001 |                         |

| <ul> <li>Better solution<br/>meaningful MI<br/>branch/jump a</li> </ul>           | PS instr                             | uctions (fix                                                                     | the<br>sters)           |

| CS 61C L17 Introduction to MIPS: Instruction                                      | on Representation III (8)            |                                                                                  | Garcia, Fall 2004 © UCB |

| Decoding Exa                         | ample (               | 6/7)                                                                                          |                         |

|--------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------|-------------------------|

| • MIPS Assen                         | nbly (P               | art 2):                                                                                       |                         |

| Loop :                               | addi                  | <pre>\$v0,\$0,\$0 \$t0,\$0,\$a1 \$t0,\$0,Exit \$t0,\$0,Exit \$v0,\$v0,\$a0 \$a1,\$a1,-1</pre> |                         |

| Exit:                                | j                     | Loop                                                                                          |                         |

| •Next step: to<br>(be creative       |                       | e to C code                                                                                   |                         |

| CS 61C L17 Introduction to MIPS: Int | truction Representati | on III (9)                                                                                    | Garcia, Fall 2004 © UCB |

| Decoding E                                                                    | Example (7/7)                                                                                                                                                 |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $00001025_{hex}$<br>$0005402A_{hex}$<br>$11000003_{hex}$                      | After C code (Mapping below)<br>\$v0: product<br>\$a0: multiplicand<br>\$a1: multiplier<br>product = 0;                                                       |

| 00441020 <sub>hex</sub><br>20A5FFFF <sub>hex</sub><br>08100001 <sub>hex</sub> | <pre>while (multiplier &gt; 0) {     product += multiplicand;     multiplier -= 1; } ,\$0,\$0</pre>                                                           |

| Loop: slt \$t(<br>beq \$t(<br>add \$v(                                        | ,\$0,\$a1     Demonstrated Big 61C       ,\$0,Exit     Idea: Instructions are       ,\$v0,\$a0     just numbers, code is       ,\$a1,-1     treated like data |

| Exit:                                                                         | ion III (10) Garcia, Fall 2004 © UC                                                                                                                           |

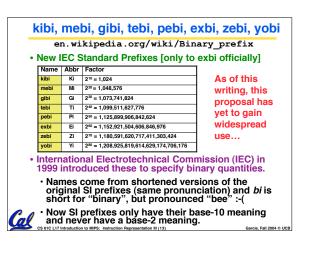

| K     | ilo, | Mega, Giga, Tera, Pe                    | ta, Exa, Zetta, Yotta                    |

|-------|------|-----------------------------------------|------------------------------------------|

| ph    | vsi  | cs.nist.gov/cuu/                        | Units/binarv.html                        |

| -     | -    | non use prefixes (all SI,               | -                                        |

| Name  | Abbr | Factor                                  | SI size                                  |

| Kilo  | к    | 2 <sup>10</sup> = 1,024                 | 10 <sup>3</sup> = 1,000                  |

| Mega  | м    | 2 <sup>20</sup> = 1,048,576             | 106 = 1,000,000                          |

| Giga  | G    | 2 <sup>30</sup> = 1,073,741,824         | 10 <sup>9</sup> = 1,000,000,000          |

| Tera  | т    | 2 <sup>40</sup> = 1,099,511,627,776     | 10 <sup>12</sup> = 1,000,000,000,000     |

| Peta  | Р    | 2 <sup>50</sup> = 1,125,899,906,842,624 | 1015 = 1,000,000,000,000,000             |

| Exa   | E    | 260 = 1,152,921,504,606,846,976         | 1018 = 1,000,000,000,000,000,000         |

| Zetta | z    | 270 = 1,180,591,620,717,411,303,424     | 1021 = 1,000,000,000,000,000,000,000     |

| Yotta | Y    | 280 = 1,208,925,819,614,629,174,706,176 | 1024 = 1.000.000.000.000.000.000.000.000 |

Confusing! Common usage of "kilobyte" means 1024 bytes, but the "correct" SI value is 1000 bytes

all 2004 © UCB

CS 61C L17 Introduction to MIPS: Instruction Representation III (17)

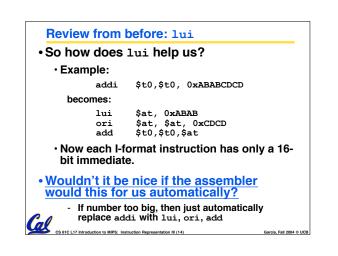

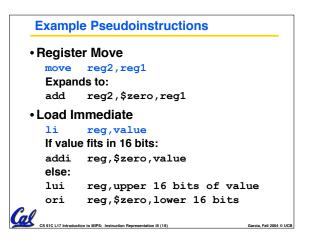

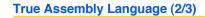

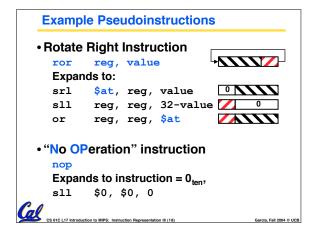

## • Problem:

- When breaking up a pseudoinstruction, the assembler may need to use an extra reg.

- If it uses any regular register, it'll overwrite whatever the program has put into it.

## Solution:

- Reserve a register (\$1, called \$at for "assembler temporary") that assembler will use to break up pseudo-instructions.

- Since the assembler may use this at any time, it's not safe to code with it.

Garcia, Fall 2004 © UCB

| Rewrite TAL                         | as MAL                               | -              |                         |

|-------------------------------------|--------------------------------------|----------------|-------------------------|

| •TAL:                               |                                      |                |                         |

| Loop:<br>Exit:                      | or<br>slt<br>beq<br>add<br>addi<br>j | \$v0,\$v0,\$a0 |                         |

| • This time c                       | onvert                               | o MAL          |                         |

| • It's OK for t<br>make up M        |                                      |                |                         |

| CS 61C L17 Introduction to MIPS: In | nstruction Representati              | on III (22)    | Garcia, Fall 2004 © UCB |

| Rewrite TAL                     | as MA                           | L (Answer)                                                    |

|---------------------------------|---------------------------------|---------------------------------------------------------------|

| •TAL:<br>Loop:                  | or<br>slt<br>beq<br>add<br>addi | \$a1,\$a1,-1                                                  |

| Exit:                           | j                               | Loop                                                          |

| •MAL:                           |                                 |                                                               |

| Loop:                           | li<br>bge<br>add<br>sub         | <pre>\$v0,0 \$zero,\$a1,Exit \$v0,\$v0,\$a0 \$a1,\$a1,1</pre> |

| Exit:                           | j                               | Loop                                                          |

| CS 61C L17 Introduction to MIPS | : Instruction Represent         | ation III (23) Garcia, Fall 2004 © UG                         |

| Peer Instruction                                                     |                         |

|----------------------------------------------------------------------|-------------------------|

|                                                                      |                         |

|                                                                      |                         |

|                                                                      |                         |

| Which of the instructions below are MAL and which are TAL?           | ABC<br>1: MMM<br>2: MMT |

| A.addi \$t0, \$t1, 40000                                             | 3: MTM<br>4: MTT        |

| B.beq \$s0, 10, Exit                                                 | 5: TMM<br>6: TMT        |

| C.sub \$t0, \$t1, 1                                                  | 7: TTM<br>8: TTT        |

| CS 61C L17 Introduction to MIPS: Instruction Representation III (24) | Garcia, Fall 2004 © UCB |

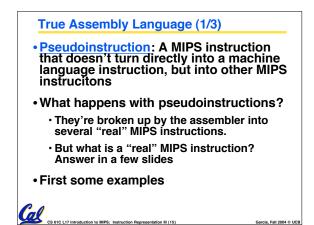

| • Disassembly is simple and a decoding opcode field.       | starts by          |

|------------------------------------------------------------|--------------------|

| ullet Be creative, efficient when a                        | uthoring C         |

| Assembler expands real ins<br>(TAL) with pseudoinstruction |                    |

| <ul> <li>Only TAL can be converted to</li> </ul>           | o raw binary       |

| <ul> <li>Assembler's job to do conve</li> </ul>            | rsion              |

| <ul> <li>Assembler uses reserved reg</li> </ul>            | <b>jister</b> \$at |

| <ul> <li>MAL makes it <u>much</u> easier to</li> </ul>     | write MIPS         |