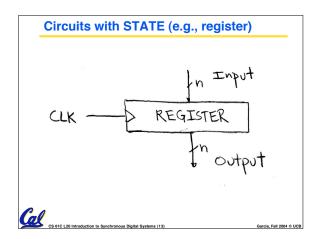

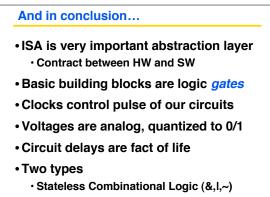

• A *combinational* logic block is one in which the output is a function only of its current input.

Garcia, Fall 2004 © UCB

• Combinational logic cannot have memory (e.g., a register is not a combinational unit).

CS 61C L20 Inf

|    | Peer Instruction                                                                                                                          |                      |                                        |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

|    |                                                                                                                                           |                      |                                        |

| Α. | SW can peek at HW (past ISA                                                                                                               |                      | ABC                                    |

| Α. | SW can peek at HW (past ISA abstraction boundary) for optimizations                                                                       | 1:                   | ABC<br>FFF                             |

|    | abstraction boundary) for optimizations                                                                                                   | 2:                   | FFF<br>FFT                             |

|    | abstraction boundary) for optimizations<br>SW can depend on particular HW                                                                 | 2:<br>3:             | FFF<br>FFT<br>FTF                      |

|    | abstraction boundary) for optimizations                                                                                                   | 2:<br>3:<br>4:       | FFF<br>FFT<br>FTF<br>FTT               |

| В. | abstraction boundary) for optimizations<br>SW can depend on particular HW<br>implementation of ISA                                        | 2:<br>3:<br>4:<br>5: | FFF<br>FFT<br>FTF<br>FTT<br>TFF        |

| В. | abstraction boundary) for optimizations<br>SW can depend on particular HW<br>implementation of ISA<br>Timing diagrams serve as a critical | 2:<br>3:<br>4:       | FFF<br>FFT<br>FTF<br>FTT<br>TFF<br>TFT |

| В. | abstraction boundary) for optimizations<br>SW can depend on particular HW<br>implementation of ISA                                        | 2:<br>3:<br>4:<br>5: | FFF<br>FFT<br>FTF<br>FTT<br>TFF        |

Garcia, Fall 2004 © UCB

• State circuits (e.g., registers)