## Review...

- We use feedback to maintain state

- Register files used to build memories

- D-FlipFlops used for Register files

- Clocks usually tied to D-FlipFlop load

Setup and Hold times important

- Pipeline big-delay CL for faster clock

CS 6IC L12 Representations of Combinatorial Logic Circuits (2)

• Finite State Machines extremely useful • You'll see them again in 150, 152 & 164

Garcia, Spring 2004 © UCB

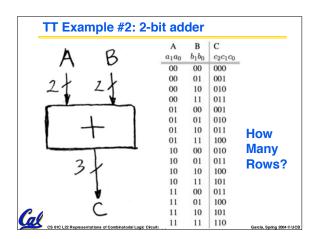

| TT Example                       | #3: 32-bit uns                 | signed adder              |  |  |

|----------------------------------|--------------------------------|---------------------------|--|--|

| Α                                | В                              | C                         |  |  |

| 000 0                            | 000 0                          | 000 00                    |  |  |

| 000 0                            | 000 1                          | 000 01                    |  |  |

|                                  |                                | • How                     |  |  |

|                                  |                                | . Many<br>Rows?           |  |  |

|                                  |                                | •                         |  |  |

| 111 1                            | 111 1                          | 111 10                    |  |  |

| CS 61C L22 Representations of Co | mbinatorial Logic Circuits (7) | Garcia, Spring 2004 @ UCI |  |  |

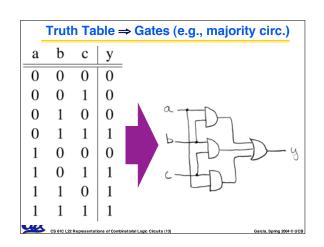

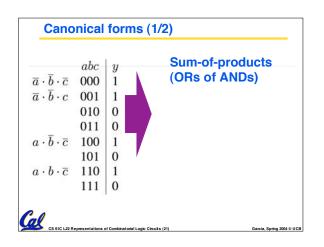

| TT Example #3: 3-input majority circuit |                |               |     |                            |  |  |

|-----------------------------------------|----------------|---------------|-----|----------------------------|--|--|

|                                         | а              | b             | с   | У                          |  |  |

|                                         | 0              | 0             | 0   | 0                          |  |  |

|                                         | 0              | 0             | 1   | 0                          |  |  |

|                                         | 0              | 1             | 0   | 0                          |  |  |

|                                         | 0              | 1             | 1   | 1                          |  |  |

|                                         | 1              | 0             | 0   | 0                          |  |  |

|                                         | 1              | 0             | 1   | 1                          |  |  |

|                                         | 1              | 1             | 0   | 1                          |  |  |

| C                                       | 1              | 1             | 1   | 1                          |  |  |

| CS 61C L22 Representations of C         | ombinatorial L | ogic Circuits | (8) | Garcia, Spring 2004 © U CB |  |  |

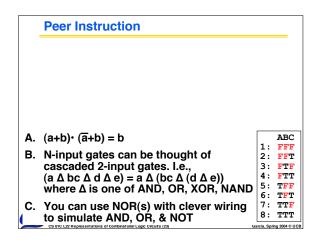

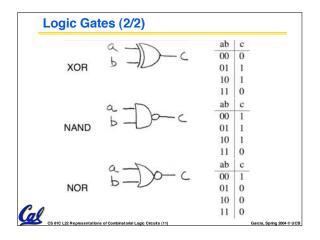

| 2-input gates extend to n-inputs                                       |   |   |   |                         |  |  |

|------------------------------------------------------------------------|---|---|---|-------------------------|--|--|

| N-input XOR is the                                                     | a | b | с | y                       |  |  |

| only one which isn't<br>so obvious                                     | 0 | 0 | 0 | 0                       |  |  |

| <ul> <li>It's simple: XOR is a<br/>1 iff the # of 1s at its</li> </ul> | 0 | 0 | 1 | 1                       |  |  |

| 1 iff the # of 1s at its input is odd ⇒                                | 0 | 1 | 0 | 1                       |  |  |

|                                                                        | 0 | 1 | 1 | 0                       |  |  |

|                                                                        | 1 | 0 | 0 | 1                       |  |  |

|                                                                        | 1 | 0 | 1 | 0                       |  |  |

|                                                                        | 1 | 1 | 0 | 0                       |  |  |

| 201                                                                    | 1 | 1 | 1 | 1                       |  |  |

| CS 61C L22 Representations of Combinatorial Logic Circuits (12)        |   |   |   | Garcia, Spring 2004 © U |  |  |