# inst.eecs.berkeley.edu/~cs61c CS61C : Machine Structures

#### Lecture 22 – Representations of Combinatorial Logic Circuits

2004-10-20

#### **Lecturer PSOE Dan Garcia**

www.cs.berkeley.edu/~ddgarcia

E-voting talk today At 4pm in 306 Soda SU Prof. David Dill will give a talk about important issues in electronic voting. This affects us all! Get there early...

CS 61C L22 Representations of Combinatorial Logic Circuits (1)

www.verifiedvoting.org

votingintegrity.com

- We use feedback to maintain state

- Register files used to build memories

- D-FlipFlops used for Register files

- Clocks usually tied to D-FlipFlop load

Setup and Hold times important

- Pipeline big-delay CL for faster clock

- Finite State Machines extremely useful

- You'll see them again in 150, 152 & 164

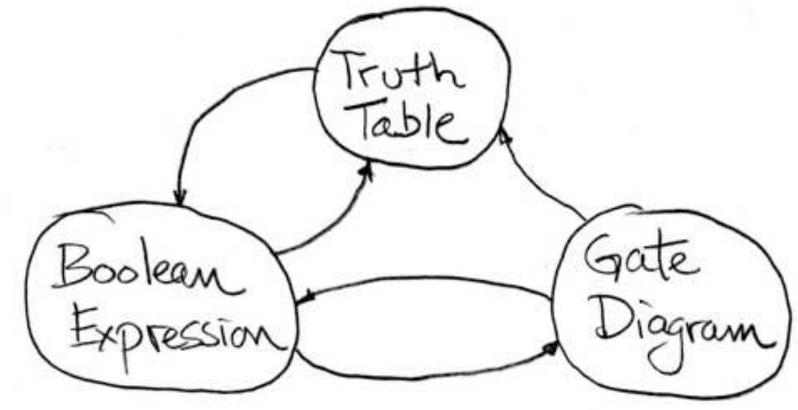

#### **Representations of CL Circuits...**

- Truth Tables

- Logic Gates

- Boolean Algebra

#### **Truth Tables**

|                                | a | b | с | d | у          |

|--------------------------------|---|---|---|---|------------|

|                                | 0 | 0 | 0 | 0 | F(0,0,0,0) |

|                                | 0 | 0 | 0 | 1 | F(0,0,0,1) |

|                                | 0 | 0 | 1 | 0 | F(0,0,1,0) |

|                                | 0 | 0 | 1 | 1 | F(0,0,1,1) |

| a                              | 0 | 1 | 0 | 0 | F(0,1,0,0) |

|                                | 0 | 1 | 0 | 1 | F(0,1,0,1) |

|                                | 0 | 1 | 1 | 0 | F(0,1,1,0) |

|                                | 0 | 1 | 1 | 1 | F(0,1,1,1) |

|                                | 1 | 0 | 0 | 0 | F(1,0,0,0) |

| $\alpha \longrightarrow \beta$ | 1 | 0 | 0 | 1 | F(1,0,0,1) |

|                                | 1 | 0 | 1 | 0 | F(1,0,1,0) |

|                                | 1 | 0 | 1 | 1 | F(1,0,1,1) |

|                                | 1 | 1 | 0 | 0 | F(1,1,0,0) |

|                                | 1 | 1 | 0 | 1 | F(1,1,0,1) |

|                                | 1 | 1 | 1 | 0 | F(1,1,1,0) |

|                                | 1 | 1 | 1 | 1 | F(1,1,1,1) |

|                                |   |   |   |   |            |

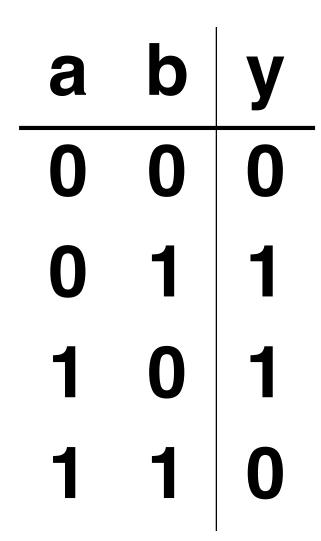

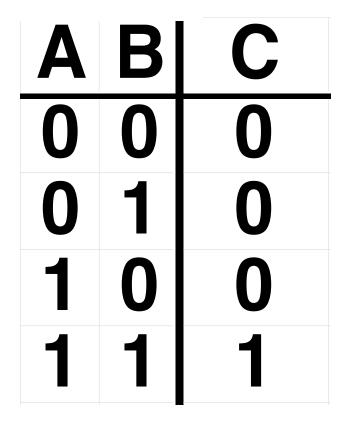

#### TT Example #1: 1 iff one (not both) a,b=1

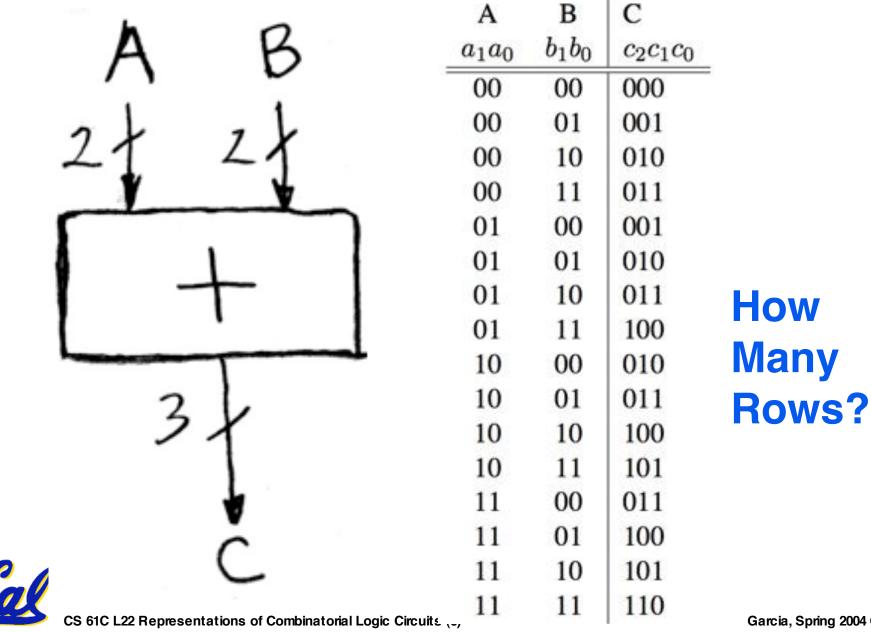

#### **TT Example #2: 2-bit adder**

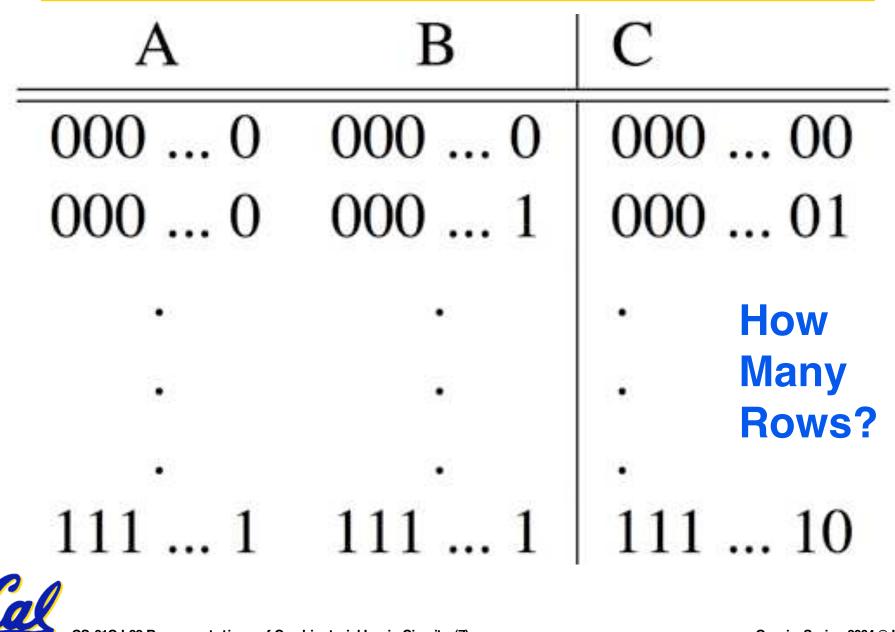

#### TT Example #3: 32-bit unsigned adder

CS 61C L22 Representations of Combinatorial Logic Circuits (7)

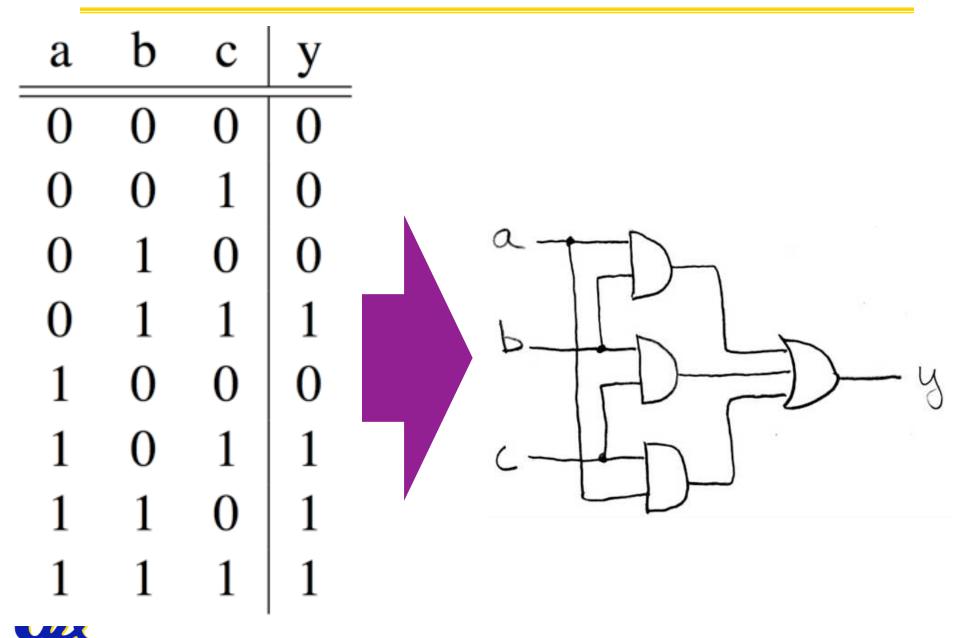

### **TT Example #3: 3-input majority circuit**

| a | b | c | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

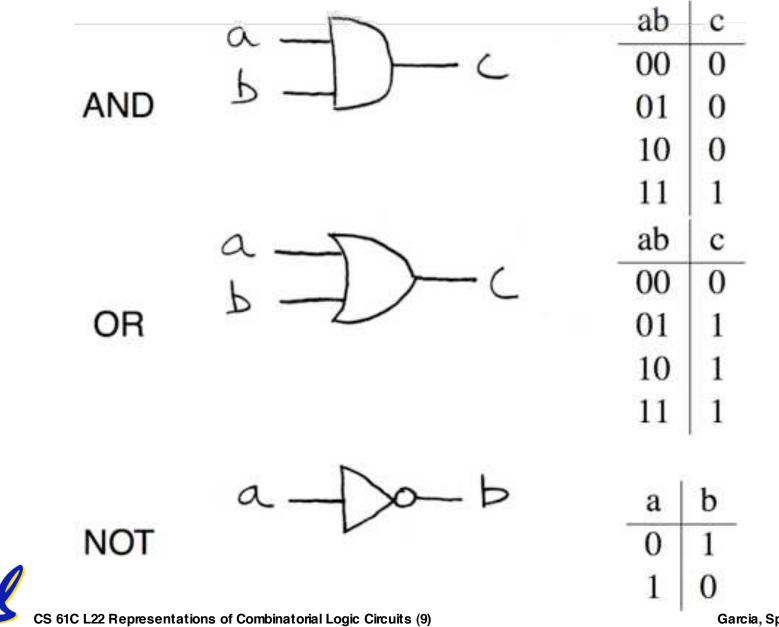

# Logic Gates (1/2)

#### And vs. Or review – Dan's mnemonic

#### AND Gate

#### Definition

CS 61C L22 Representations of Combinatorial Logic Circuits (10)

# Logic Gates (2/2)

|      | a -m                                   | ab | c |

|------|----------------------------------------|----|---|

| XOR  | $()) \rightarrow c$                    | 00 | 0 |

|      | DI                                     | 01 | 1 |

|      |                                        | 10 | 1 |

|      |                                        | 11 | 0 |

|      | a _                                    | ab | c |

| NAND | L D-C                                  | 00 | 1 |

|      |                                        | 01 | 1 |

|      |                                        | 10 | 1 |

|      |                                        | 11 | 0 |

|      | 0-5                                    | ab | c |

| NOR  | - 1) x - C                             | 00 | 1 |

|      |                                        | 01 | 0 |

|      |                                        | 10 | 0 |

|      |                                        | 11 | 0 |

|      | a of Compliant and Logic Obscribe (11) |    |   |

CS 61C L22 Representations of Combinatorial Logic Circuits (11)

# 2-input gates extend to n-inputs

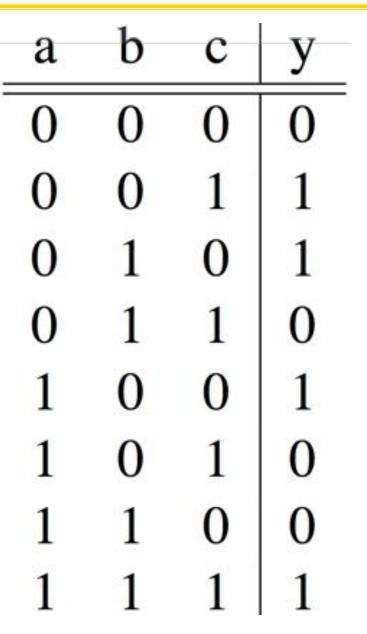

- N-input XOR is the only one which isn't so obvious

- It's simple: XOR is a 1 iff the # of 1s at its input is odd ⇒

CS 61C L22 Representations of Combinatorial Logic Circuits (12)

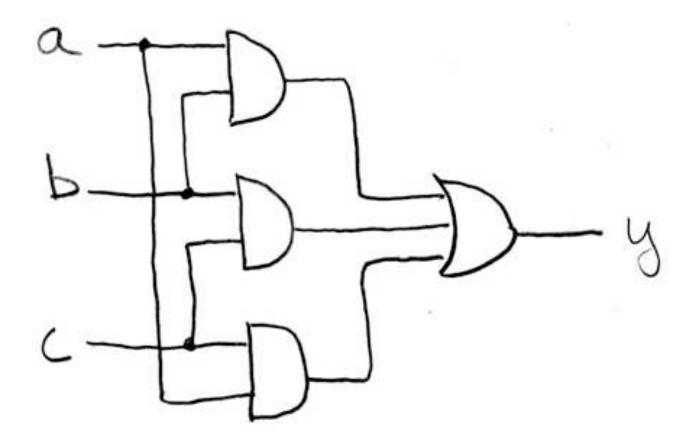

#### Truth Table ⇒ Gates (e.g., majority circ.)

CS 61C L22 Representations of Combinatorial Logic Circuits (13)

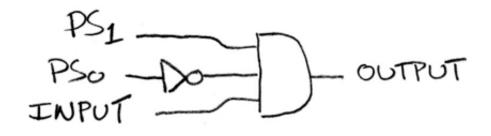

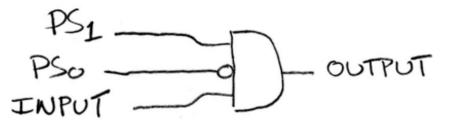

#### Truth Table ⇒ Gates (e.g., FSM circ.)

| PS | Input | NS | Output |

|----|-------|----|--------|

| 00 | 0     | 00 | 0      |

| 00 | 1     | 01 | 0      |

| 01 | 0     | 00 | 0      |

| 01 | 1     | 10 | 0      |

| 10 | 0     | 00 | 0      |

| 10 | 1     | 00 | 1      |

#### or equivalently...

# **Boolean Algebra**

- George Boole, 19<sup>th</sup> Century mathematician

- Developed a mathematical system (algebra) involving lógic

- later known as "Boolean Algebra"

- Primitive functions: AND, OR and NOT

- The power of BA is there's a one-to-one correspondence between circuits made up of AND, OR and NOT gates and equations in BA

# **Boolean Algebra (e.g., for majority fun.)**

$y = a \cdot b + a \cdot c + b \cdot c$

y = ab + ac + bc

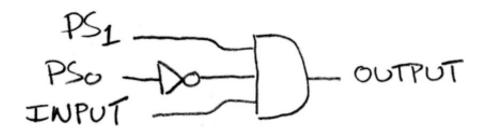

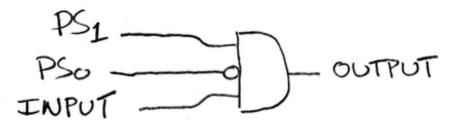

# **Boolean Algebra (e.g., for FSM)**

| PS | Input | NS | Output |

|----|-------|----|--------|

| 00 | 0     | 00 | 0      |

| 00 | 1     | 01 | 0      |

| 01 | 0     | 00 | 0      |

| 01 | 1     | 10 | 0      |

| 10 | 0     | 00 | 0      |

| 10 | 1     | 00 | 1      |

#### or equivalently...

# $y = PS_1 \cdot \overline{PS_0} \cdot INPUT$

CS 61C L22 Representations of Combinatorial Logic Circuits (17)

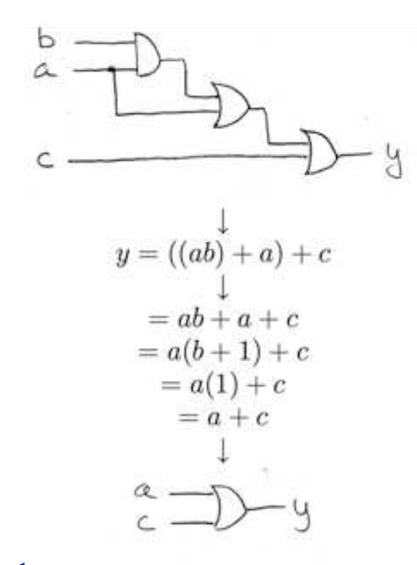

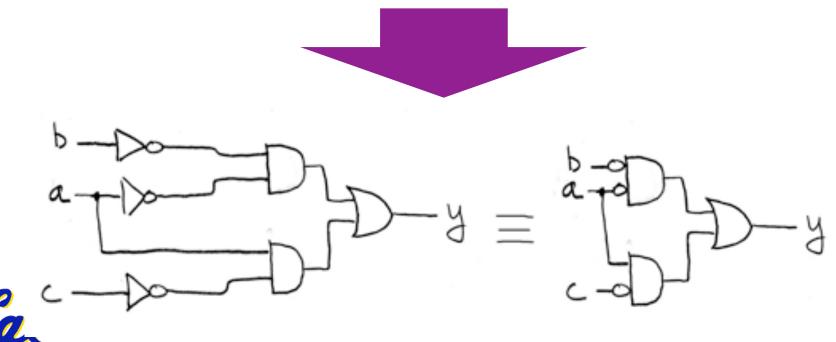

## **BA: Circuit & Algebraic Simplification**

original circuit

equation derived from original circuit

algebraic simplification

BA also great for circuit <u>verification</u> Circ X = Circ Y? use BA to prove!

simplified circuit

#### Laws of Boolean Algebra

complementarity laws of 0's and 1's identities idempotent law commutativity associativity distribution uniting theorem DeMorgan's Law

#### **Boolean Algebraic Simplification Example**

$$y = ab + a + c$$

=  $a(b+1) + c$  distribution, identity

=  $a(1) + c$  law of 1's

=  $a + c$  identity

# **Canonical forms (1/2)**

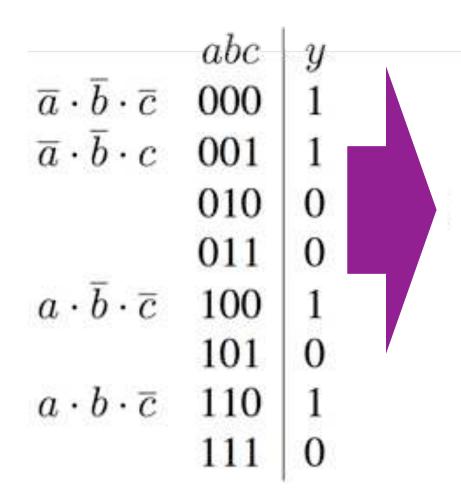

#### Sum-of-products (ORs of ANDs)

# **Canonical forms (2/2)**

$$\begin{array}{ll} y &= \overline{a}\overline{b}\overline{c} + \overline{a}\overline{b}c + a\overline{b}\overline{c} + ab\overline{c} \\ &= \overline{a}\overline{b}(\overline{c} + c) + a\overline{c}(\overline{b} + b) & distribution \\ &= \overline{a}\overline{b}(1) + a\overline{c}(1) & complementarity \\ &= \overline{a}\overline{b} + a\overline{c} & identity \end{array}$$

CS 61C L22 Representations of Combinatorial Logic Circuits (22)

- A.  $(a+b) \cdot (\overline{a}+b) = b$

- B. N-input gates can be thought of cascaded 2-input gates. I.e.,  $(a \Delta bc \Delta d \Delta e) = a \Delta (bc \Delta (d \Delta e))$ where  $\Delta$  is one of AND, OR, XOR, NAND

- C. You can use NOR(s) with clever wiring to simulate AND, OR, & NOT

CS 61C L22 Representations of Combinatorial Logic Circuits (23)

Garcia, Spring 2004 © UCB

ABC

ननन

FFT

$\mathbf{T}\mathbf{T}\mathbf{T}$

FTT

קקע

TFT

ጥጥፑ

ጥጥጥ

2.

२・

5.

**6** ·

"And In conclusion..."

• Use this table and techniques we learned to transform from 1 to another