| Peer In                 | truction Correction                                                         |

|-------------------------|-----------------------------------------------------------------------------|

| Α.                      | (a+b) ⋅ (ā+b) =?= b                                                         |

| (a+b)∙( <del>a</del> +b |                                                                             |

| aā+ab+bā-               | bb distribution                                                             |

| 0+b(a+ā)+I              | <i>complimentarity,<br/>commutativity,<br/>distribution,<br/>idempotent</i> |

| b(1)+b                  | identity, complimentarity                                                   |

| b+b                     | identity                                                                    |

| CS 61C L23 Combina      | idempotent<br>aLog: Bicks (3) Garcia Fail 204 © UCB                         |

| Peer Instruction                                                                                                    |                                                          |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                                                                                     |                                                          |

|                                                                                                                     |                                                          |

|                                                                                                                     |                                                          |

|                                                                                                                     |                                                          |

|                                                                                                                     |                                                          |

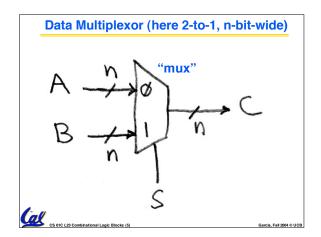

| A. Truth table for mux with 4-bits of                                                                               | ABC<br>1: FFF                                            |

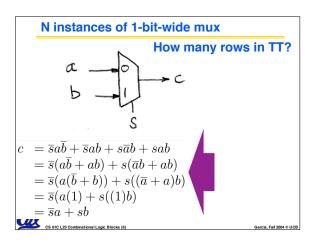

| A. Truth table for mux with 4-bits of signals is 2 <sup>4</sup> rows long                                           |                                                          |

| signals is 2 <sup>4</sup> rows long                                                                                 | 1: FFF<br>2: FFT                                         |

| signals is 2 <sup>4</sup> rows long<br>B. We could cascade N 1-bit shifters                                         | 1: FFF<br>2: FFT<br>3: FTF<br>4: FTT                     |

| signals is 2 <sup>4</sup> rows long                                                                                 | 1: FFF<br>2: FFT<br>3: FTF<br>4: FTT<br>5: TFF           |

| signals is 2 <sup>4</sup> rows long<br>B. We could cascade N 1-bit shifters<br>to make 1 N-bit shifter for sII, srl | 1: FFF<br>2: FFT<br>3: FTF<br>4: FTT<br>5: TFF<br>6: TFT |

| signals is 2 <sup>4</sup> rows long<br>B. We could cascade N 1-bit shifters                                         | 1: FFF<br>2: FFT<br>3: FTF<br>4: FTT<br>5: TFF           |

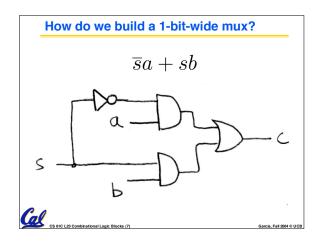

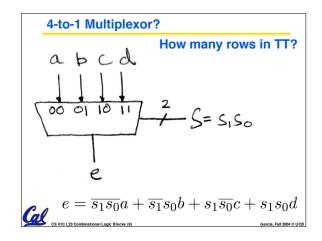

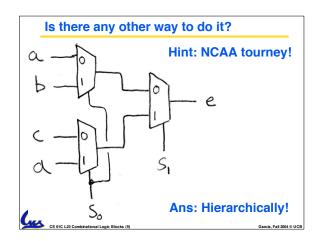

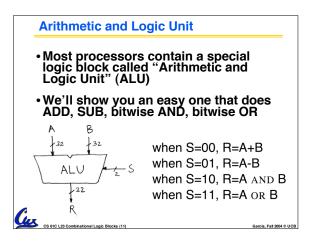

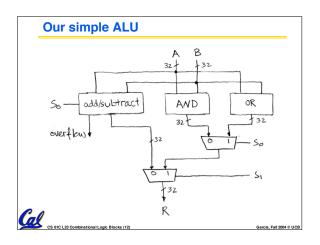

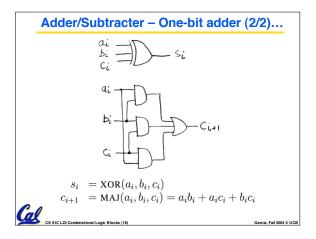

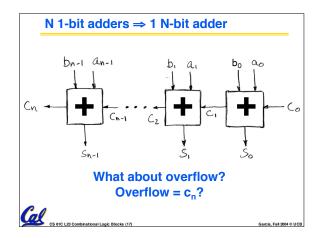

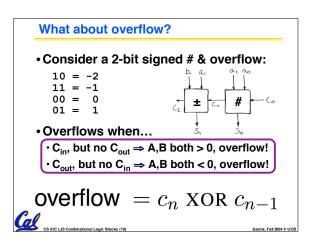

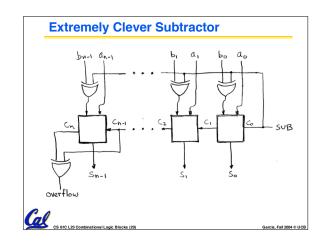

## "And In conclusion..." Use muxes to select among input S input bits selects 2S inputs Each input can be n-bits wide, indep of S Implement muxes hierarchically ALU can be implemented using a mux Coupled with basic block elements N-bit adder-subtractor done using N 1-bit adders with XOR gates on input XOR serves as conditional inverter