**Administrivia**

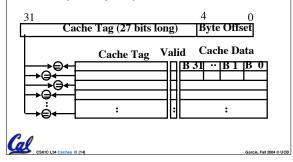

### Fully Associative Cache (1/3)

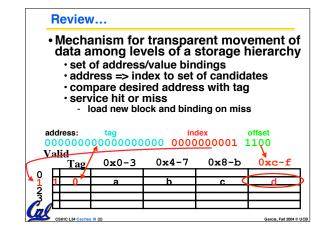

• Memory address fields:

- Tag: same as before

- Offset: same as before

- Index: non-existant

- What does this mean?

- no "rows": any block can go anywhere in the cache

- must compare with all tags in entire cache to see if data is there

Garcia, Fall 2004 © UCB

Garcia, Fall 2004 © UCB

Garcia, Fall 2004 © UCB

### Fully Associative Cache (2/3)

• Fully Associative Cache (e.g., 32 B block) • compare tags in parallel

# Fully Associative Cache (3/3)

CSEIC L34 Caches III (13)

- Benefit of Fully Assoc Cache

No Conflict Misses (since data can go anywhere)

- Drawbacks of Fully Assoc Cache

- Need hardware comparator for every single entry: if we have a 64KB of data in cache with 4B entries, we need 16K comparators: infeasible

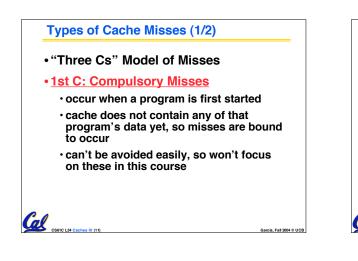

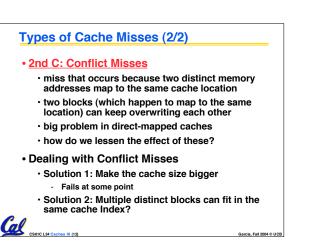

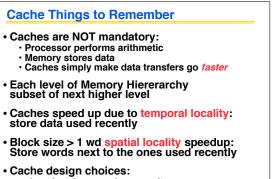

# Third Type of Cache Miss

#### Capacity Misses

- miss that occurs because the cache has a limited size

- miss that would not occur if we increase the size of the cache

Garcia, Fall 2004 © UCB

Garcia, Fall 2004 © UCB

- sketchy definition, so just get the general idea

- This is the primary type of miss for Fully Associative caches.

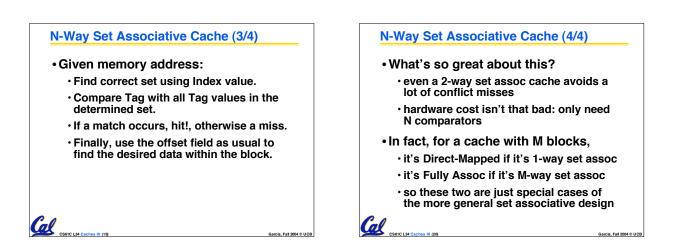

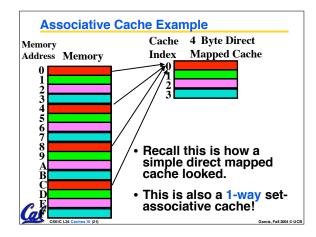

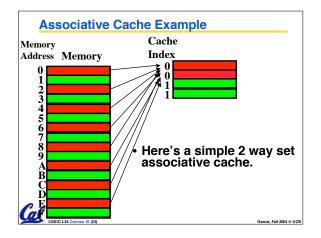

# N-Way Set Associative Cache (1/4)

### • Memory address fields:

CSEIC L34 Caches III (15)

CS61C L34 Caches III (17)

- Tag: same as before

- · Offset: same as before

- Index: points us to the correct "row" (called a <u>set</u> in this case)

#### So what's the difference?

- · each set contains multiple blocks

- once we've found correct set, must compare with all tags in that set to find our data

# N-Way Set Associative Cache (2/4)

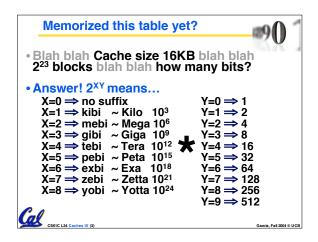

• Summary:

CS61C L34 Caches III (18)

CS61C L34 Caches III (16)

- · cache is direct-mapped w/respect to sets

- · each set is fully associative

- basically N direct-mapped caches working in parallel: each has its own valid bit and data

|          | Peer Instructions                                                                                                                       |                      |                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------|

|          |                                                                                                                                         |                      |                                 |

|          |                                                                                                                                         |                      |                                 |

|          |                                                                                                                                         |                      |                                 |

|          |                                                                                                                                         |                      |                                 |

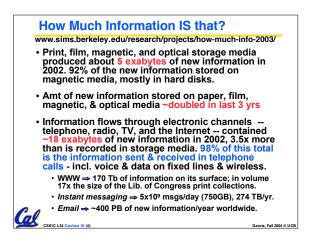

| 1.       | In the last 10 years, the gap between the                                                                                               |                      | ABC                             |

| 1.       | In the last 10 years, the gap between the<br>access time of DRAMs & the cycle time of                                                   | 1:                   | FFF                             |

| 1.       |                                                                                                                                         | 2:                   | FFF<br>FFT                      |

| 1.<br>2. | access time of DRAMs & the cycle time of processors has decreased. (I.e., is closing)                                                   |                      | FFF                             |

|          | access time of DRAMs & the cycle time of                                                                                                | 2:<br>3:             | FFF<br>FFT<br>FTF               |

|          | access time of DRAMs & the cycle time of<br>processors has decreased. (I.e., is closing)<br>A direct-mapped \$ will never out-perform a | 2:<br>3:<br>4:       | FFF<br>FFT<br>FTF<br>FTT        |

|          | access time of DRAMs & the cycle time of<br>processors has decreased. (I.e., is closing)<br>A direct-mapped \$ will never out-perform a | 2:<br>3:<br>4:<br>5: | FFF<br>FFT<br>FTF<br>FTT<br>TFF |

N-way set assoc: choice of N (direct-mapped, fully-associative just special cases for N) hes III (25) arcia, Fall 2004 © UCB