### Block Replacement Policy (1/2)

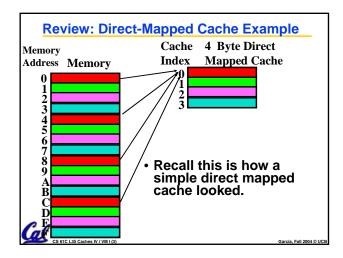

- Direct-Mapped Cache: index completely specifies position which position a block can go in on a miss

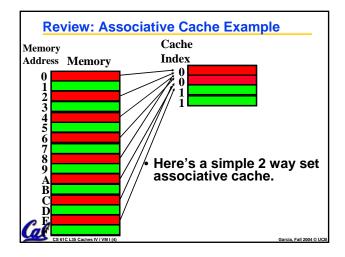

- N-Way Set Assoc: index specifies a set, but block can occupy any position within the set on a miss

- Fully Associative: block can be written into any position

- Question: if we have the choice, where should we write an incoming block?

Garcia, Fall 2004 © UCE

CS 61C L35 Caches IV / VM I (5

# Block Replacement Policy (2/2) If there are any locations with valid bit off (empty), then usually write the new block into the first one. If all possible locations already have a valid block, we must pick a replacement policy: rule by which we determine which block gets "cached out" on a miss.

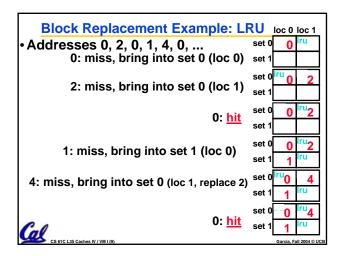

### Block Replacement Policy: LRU LRU (Least Recently Used) Idea: cache out block which has been accessed (read or write) least recently Pro: temporal locality ⇒ recent past use implies likely future use: in fact, this is a very effective policy Con: with 2-way set assoc, easy to keep track (one LRU bit); with 4-way or greater, requires complicated hardware and much time to keep track of this

Cal

# Block Replacement Example We have a 2-way set associative cache with a four word *total* capacity and one word blocks. We perform the following word accesses (ignore bytes for this problem): 0, 2, 0, 1, 4, 0, 2, 3, 5, 4 How many hits and how many misses will there be for the LRU block replacement policy?

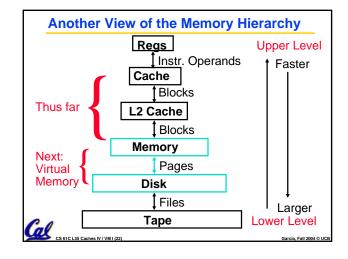

### Memory Hierarchy Requirements

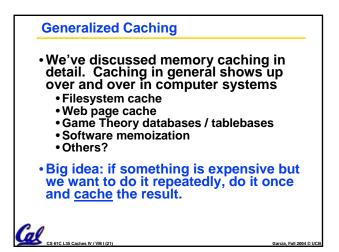

- If Principle of Locality allows caches to offer (close to) speed of cache memory with size of DRAM memory, then recursively why not use at next level to give speed of DRAM memory, size of Disk memory?

- While we're at it, what other things do we need from our memory system?

Gel CS BIC LAS

### **Memory Hierarchy Requirements**

- Share memory between multiple processes but still provide protection – don't let one program read/write memory from another

- Address space give each program the illusion that it has its own private memory

- Suppose code starts at address 0x40000000. But different processes have different code, both residing at the same address. So each program has a different view of memory.

Garcia, Fall 2004 © UCB

CS 61C L35 Caches IV / VM I (2)

### **Virtual Memory**

- Called "Virtual Memory"

- Also allows OS to share memory, protect programs from each other

- Today, more important for <u>protection</u> vs. just another level of memory hierarchy

- Historically, it predates caches

| -        | Peer Instruction                                                                                                                                   |                            |                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|

|          |                                                                                                                                                    |                            |                                        |

|          |                                                                                                                                                    |                            |                                        |

|          |                                                                                                                                                    |                            |                                        |

|          |                                                                                                                                                    |                            |                                        |

|          |                                                                                                                                                    |                            |                                        |

| 1.       | Increased associativity (1->2->4->8-way) ⇒                                                                                                         |                            | ABC                                    |

| 1.       | Increased associativity (1->2->4->8-way) $\Rightarrow$ decreased or steady miss rate.                                                              | 1:                         | ABC<br>FFF                             |

|          | decreased or steady miss rate.                                                                                                                     | 2:                         | FFF<br>FFT                             |

| 1.<br>2. | decreased or steady miss rate.<br>Increased associativity $\Rightarrow$ increased cost &                                                           | 2:<br>3:                   | FFF<br>FFT<br>FTF                      |

|          | decreased or steady miss rate.                                                                                                                     | 2:<br>3:<br>4:             | FFF<br>FFT<br>FTF<br>FTT               |

| 2.       | decreased or steady miss rate.<br>Increased associativity ⇒ increased cost & slower access time.                                                   | 2:<br>3:<br>4:<br>5:       | FFF<br>FFT<br>FTF<br>FTT<br>TFF        |

|          | decreased or steady miss rate.<br>Increased associativity ⇒ increased cost & slower access time.<br>The ratio of costs of a "miss" vs. a "hit" are | 2:<br>3:<br>4:<br>5:<br>6: | FFF<br>FFT<br>FTF<br>FTT<br>TFF<br>TFT |

| 2.       | decreased or steady miss rate.<br>Increased associativity ⇒ increased cost & slower access time.                                                   | 2:<br>3:<br>4:<br>5:       | FFF<br>FFT<br>FTF<br>FTT<br>TFF        |

### And in Conclusion...

Cal

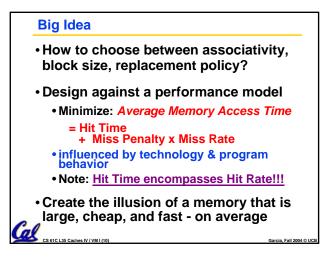

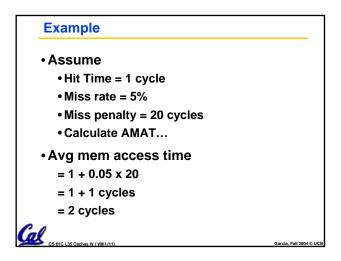

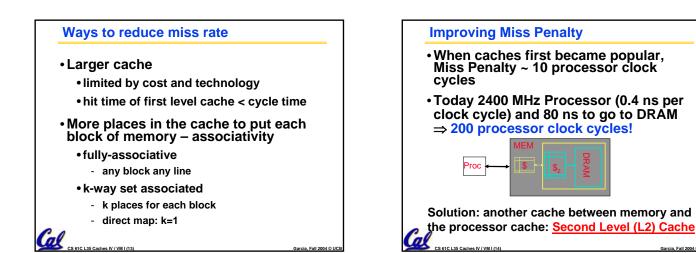

- Cache design choices:

- size of cache: speed v. capacity

- direct-mapped v. associative

- for N-way set assoc: choice of N block replacement policy

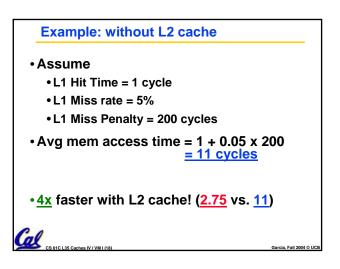

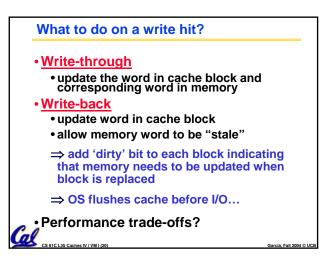

- 2nd level cache? Write through v. write back?

- Use performance model to pick between choices, depending on programs, technology, budget, ...

### Virtual Memory

• Predates caches; each process thinks it has all the memory to itself; protection! IV / VM I (2