## Review...

- •ISA is very important abstraction layer

- · Contract between HW and SW

- Basic building blocks are logic gates

- Clocks control pulse of our circuits

- Voltages are analog, quantized to 0/1

- · Circuit delays are fact of life

- Two types

- Stateless Combinational Logic (&,I,~), in which output is function of input only

- · State circuits (e.g., registers)

CS61C L21 State Elements: Circuits That Re

Garcia © U

## **Peer Instruction**

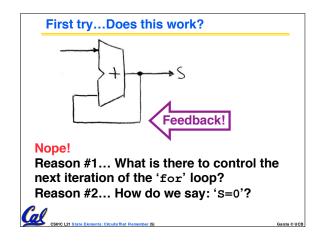

A. HW feedback akin to SW recursion ABC

1: FFF

2: FFT

3: FTF

4: FTT

5: TFF

6: TFT

7: TTF

ABC

Garcia © UCB

- B. We can implement a D-Q flipflop as simple CL (And, Or, Not gates)

- C. You can build a FSM to signal when an equal number of 0s and 1s has appeared in the input.

## "And In conclusion..."

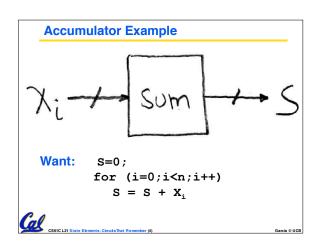

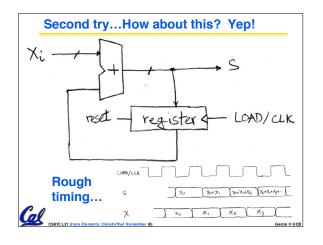

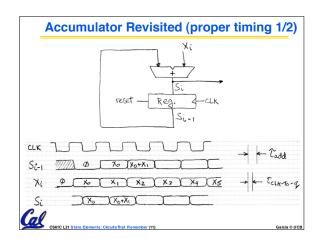

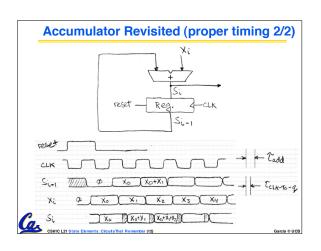

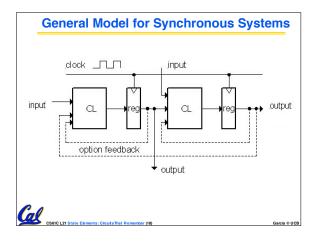

- We use feedback to maintain state

- Register files used to build memories

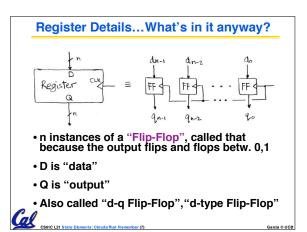

- D-FlipFlops used to build Register files

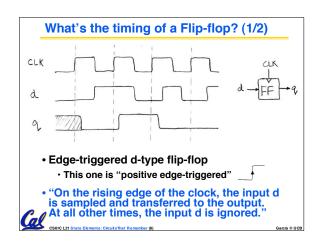

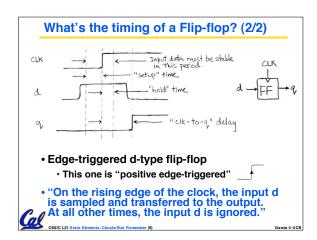

- Clocks tell us when D-FlipFlops change

- Setup and Hold times important

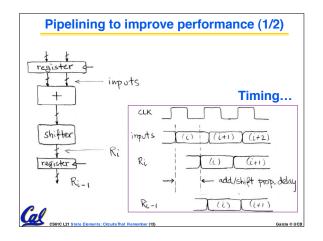

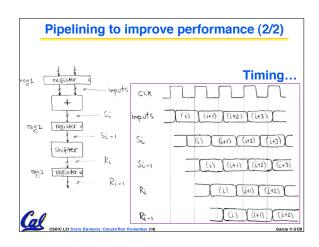

- We pipeline big-delay CL for faster clock

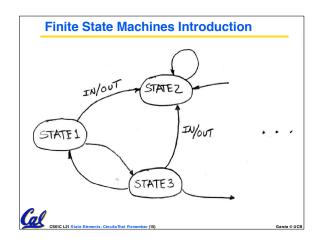

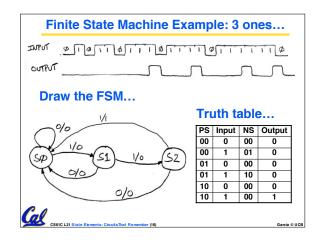

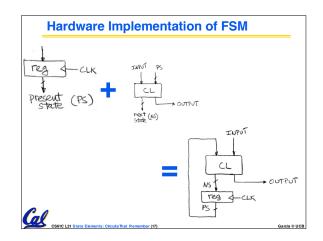

- Finite State Machines extremely useful

- · You'll see them in HW classes (150,152) & 164