www.cs.berkeley.edu/~ddgarcia Bionic Eyes let blind see! ⇒ Johns Hopkins researchers have

announced they have invented a "bionic eye" with a computer chip on the back of the eye and a small wireless video camera in a pair of glasses. Face recognition? Not yet, but soon!

news.bbc.co.uk/1/hi/health/4411591.stm

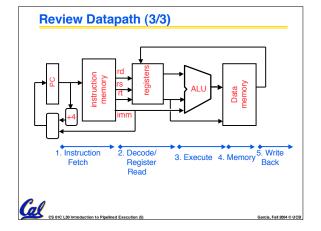

# Review: Single cycle datapath

## °5 steps to design a processor

- 1. Analyze instruction set => datapath requirements

- 2. <u>Select</u> set of datapath components & establish clock methodology

Control

Datapath

- 3. Assemble datapath meeting the requirements

- 4. <u>Analyze</u> implementation of each instruction to determine setting of control points that effects the register transfer. Processor

- 5. Assemble the control logic

# Control is the hard part

°MIPS makes that easier

CS 61C L30 Introduction to Pipelined Execution (2)

- · Instructions same size

- · Source registers always in same place

- Immediates same size, location

Operations always on registers/immediates

Garcia, Fall 2004 © UCB

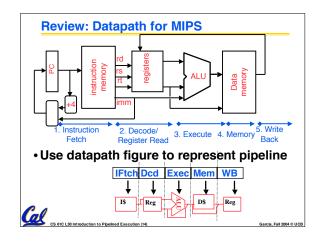

## **Review Datapath (1/3)**

- Datapath is the hardware that performs operations necessary to execute programs.

- Control instructs datapath on what to do next.

- Datapath needs:

- · access to storage (general purpose registers and memory)

- · computational ability (ALU)

- · helper hardware (local registers and PC)

# <u>Cel</u> <u>cs 61C L30 Ir</u>

# Review Datapath (2/3)

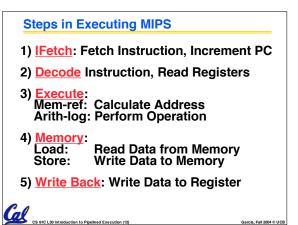

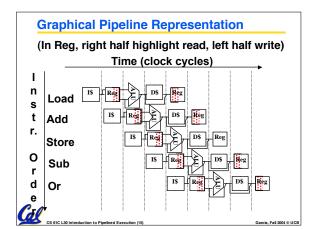

- Five stages of datapath (executing an instruction):

- 1. Instruction Fetch (Increment PC)

- 2. Instruction Decode (Read Registers)

- 3. ALU (Computation)

- 4. Memory Access

- 5. Write to Registers

- ALL instructions must go through ALL five stages.

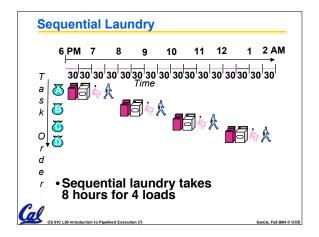

## **General Definitions**

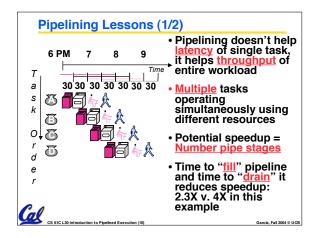

- Latency: time to completely execute a certain task

- for example, time to read a sector from disk is disk access time or disk latency

- Throughput: amount of work that can be done over a period of time

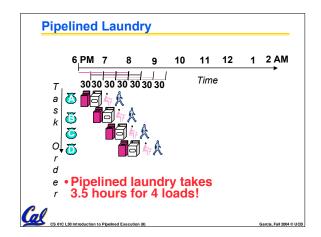

#### Pipelining Lessons (2/2) Suppose new Washer takes 20 6 PM 7 8 9 minutes, new Stasher takes 20 30 30 30 30 30 30 minutes. How much faster is pipeline? s **乙** k **5** Pipeline rate 012 limited by slowest 7 pipeline stage е Unbalanced lengths of pipe stages also reduces speedup

# **Example**

- Suppose 2 ns for memory access, 2 ns for ALU operation, and 1 ns for register file read or write; compute instr rate

- Nonpipelined Execution:

- · lw : IF + Read Reg + ALU + Memory + Write Reg = 2 + 1 + 2 + 2 + 1 = 8 ns

- add: IF + Read Reg + ALU + Write Reg = 2 + 1 + 2 + 1 = 6 ns

- Pipelined Execution:

- Max(IF,Read Reg,ALU,Memory,Write Reg)

CS 61C L30 Introduction to Pipelined Execution (16)

arcia Fall 2004 © UC

# Pipeline Hazard: Matching socks in later load 6 PM 7 8 9 10 11 12 1 2 AM 7 30 30 30 30 30 30 30 7 Time A depends on D; stall since folder tied up

# **Problems for Computers**

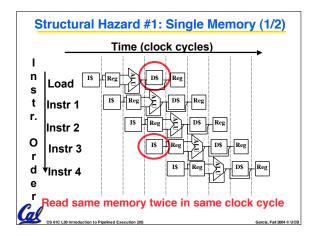

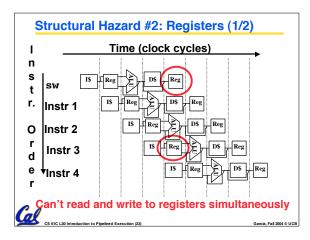

- Limits to pipelining: <u>Hazards</u> prevent next instruction from executing during its designated clock cycle

- Structural hazards: HW cannot support this combination of instructions (single person to fold and put clothes away)

- Control hazards: Pipelining of branches & other instructions stall the pipeline until the hazard; "bubbles" in the pipeline

- <u>Data hazards</u>: Instruction depends on result of prior instruction still in the pipeline (missing sock)

CS 61C L30 Introduction to Pipelined Execution (19)

Garcia, Fall 2004 © UCB

# Structural Hazard #1: Single Memory (2/2)

- Solution:

- · infeasible and inefficient to create second memory

- (We'll learn about this more next week)

- · so simulate this by having two Level 1 **Caches** (a temporary smaller [of usually most recently used] copy of memory)

- · have both an L1 Instruction Cache and an L1 Data Cache

- · need more complex hardware to control when both caches miss

CS 61C L30 Introduction to Pipelined Execution (21)

# Structural Hazard #2: Registers (2/2)

- Fact: Register access is VERY fast: takes less than half the time of ALU stage

- Solution: introduce convention

- · always Write to Registers during first half of each clock cycle

- · always Read from Registers during second half of each clock cycle

- · Result: can perform Read and Write during same clock cycle

#### **Peer Instruction**

- A. Thanks to pipelining, I have <u>reduced the time</u> it took me to wash my shirt.

- B. Longer pipelines are <u>always a win</u> (since less work per stage & a faster clock).

- We can <u>rely on compilers</u> to help us avoid data hazards by reordering instrs.

1: FFF FFT 3: FTF 4: FTT TFF TFT TTF 8: TTT Sarcia, Fall 2004 © UCB

ABC

Things to Remember

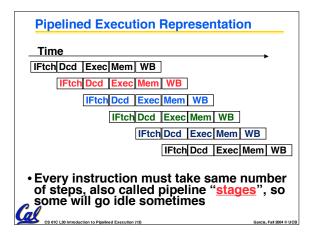

# Optimal Pipeline

- · Each stage is executing part of an instruction each clock cycle.

- · One instruction finishes during each clock cycle.

- · On average, execute far more quickly.

- · What makes this work?

- Similarities between instructions allow us to use same stages for all instructions (generally).

- · Each stage takes about the same amount of time as all others: little wasted time.