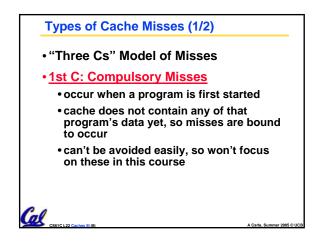

## <u>Capacity Misses</u>

- miss that occurs because the cache has a limited size

- miss that would not occur if we increase the size of the cache

- sketchy definition, so just get the general idea

- This is the primary type of miss for Fully Associative caches.

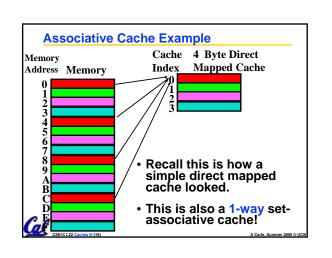

# N-Way Set Associative Cache (1/4)

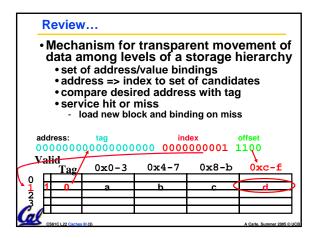

- Memory address fields:

- Tag: same as before

- Offset: same as before

- Index: points us to the correct "row" (called a <u>set</u> in this case)

- So what's the difference?

Cal

Cal

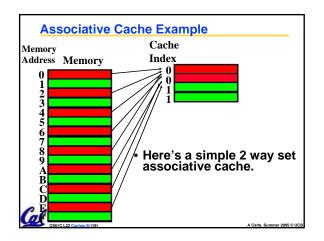

- each set contains multiple blocks

- once we've found correct set, must compare with all tags in that set to find our data

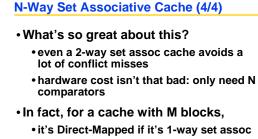

#### N-Way Set Associative Cache (2/4)

#### • Summary:

Cal

Cal

Cal

- cache is direct-mapped w/respect to sets

- each set is fully associative

- basically N direct-mapped caches working in parallel: each has its own valid bit and data

#### N-Way Set Associative Cache (3/4)

## • Given memory address:

- Find correct set using Index value.

- Compare Tag with all Tag values in the determined set.

- If a match occurs, hit!, otherwise a miss.

- Finally, use the offset field as usual to find the desired data within the block.

- it's Fully Assoc if it's M-way set assoc

- so these two are just special cases of the more general set associative design

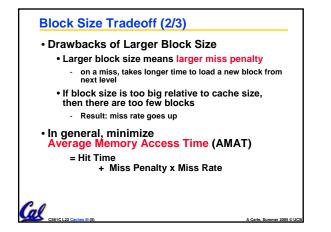

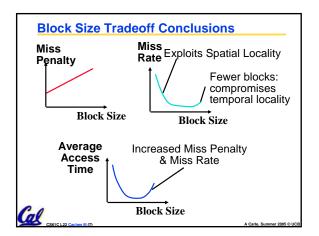

- How to choose between associativity, block size, replacement policy?

- Design against a performance model

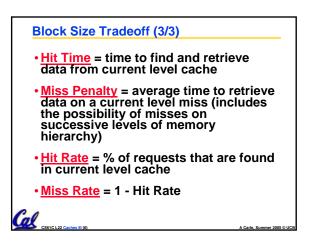

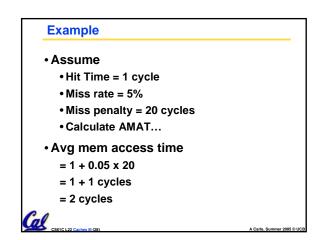

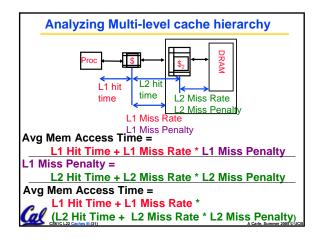

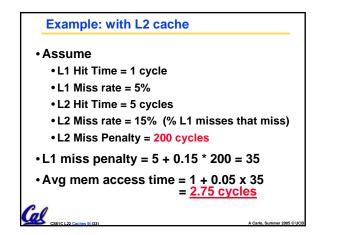

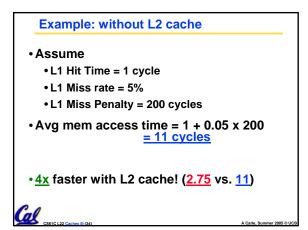

- Minimize: Average Memory Access Time = Hit Time + Miss Penalty x Miss Rate

- influenced by technology & program behavior

- Note: <u>Hit Time encompasses Hit Rate!!!</u>

- Create the illusion of a memory that is large, cheap, and fast - on average al

#### **Peer Instructions**

Cal

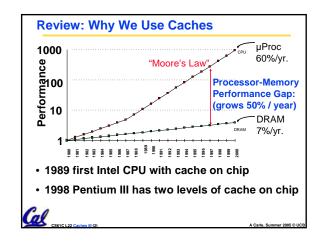

- 1. In the last 10 years, the gap between the access time of DRAMs & the cycle time of processors has decreased. (I.e., is closing)

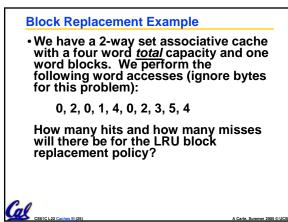

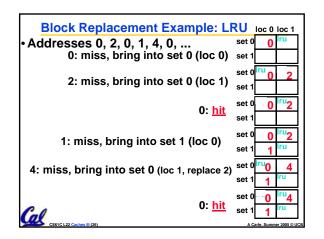

- 2. A 2-way set-associative cache can be outperformed by a direct-mapped cache.

- 3. Larger block size  $\Rightarrow$  lower miss rate

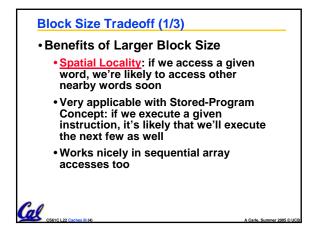

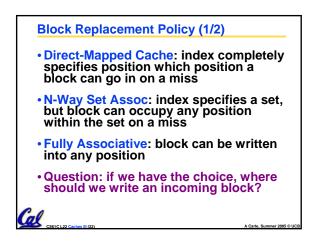

# And in Conclusion... • Cache design choices: • size of cache: speed v. capacity

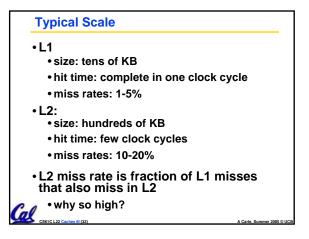

- direct-mapped v. associative

- for N-way set assoc: choice of N

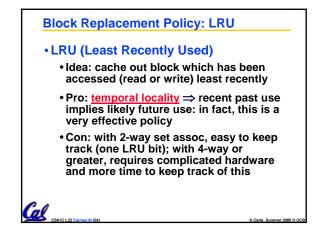

- block replacement policy

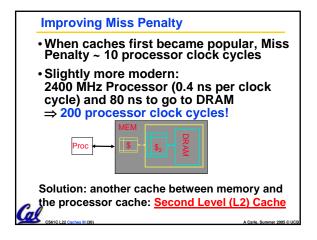

- 2<sup>nd</sup> level cache?

- 3<sup>rd</sup> level cache?

Gel CSEIC L22

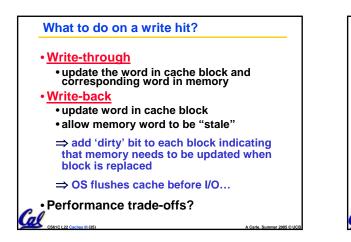

- Write through v. write back?

- Use performance model to pick between choices, depending on programs, technology, budget, ...