## **Examples of Propagation Delay**

| Product     | CMOS<br>technology<br>generation | Clock<br>frequency, <i>f</i> | Fan-out=4<br>inverter<br>delay |

|-------------|----------------------------------|------------------------------|--------------------------------|

| Pentium II  | 0.25 μm                          | 600 MHz                      | ~100 ps                        |

| Pentium III | 0.18 μm                          | 1.8 GHz                      | ~40 ps                         |

| Pentium IV  | 0.13 μm                          | 3.2 GHz                      | ~20 ps                         |

Typical clock periods:

• high-performance  $\mu P$ : ~15 FO4 delays

Instructor: Octavian Florescu

5

• PlayStation 2: 60 FO4 delays

EE40 Summer 2006: Lecture 16

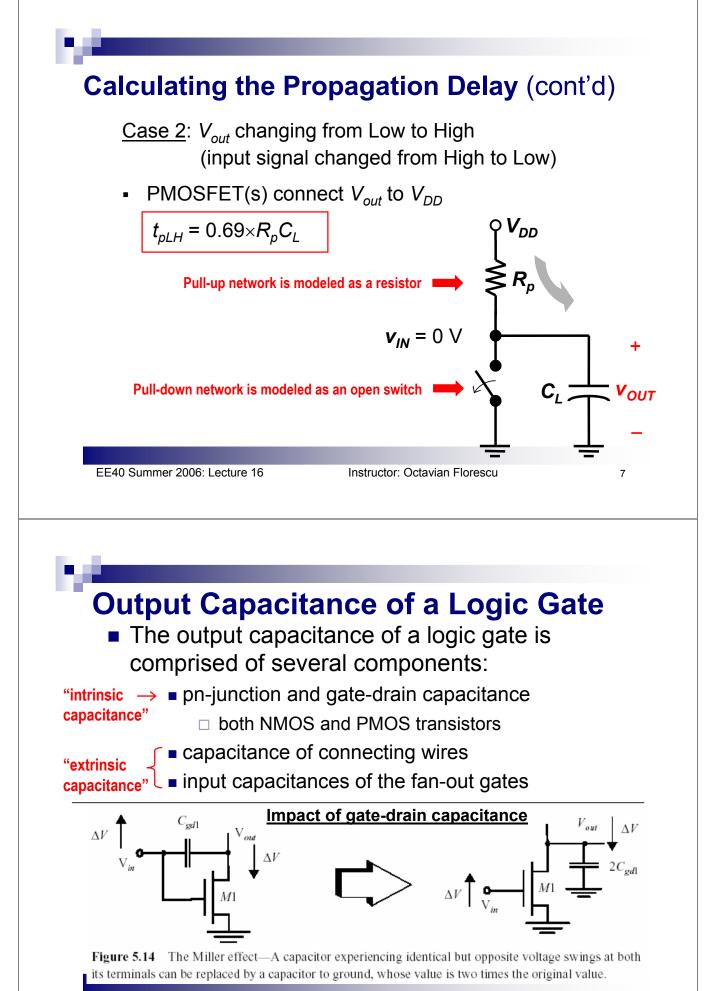

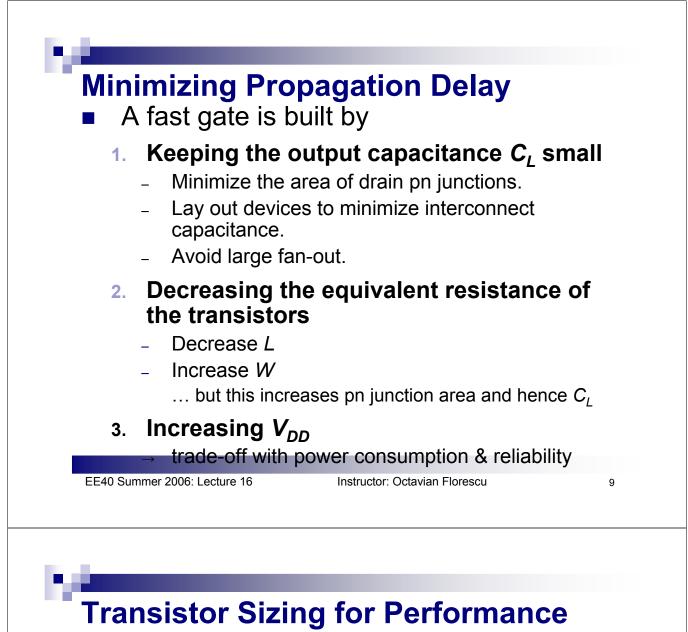

- Widening the transistors reduces resistance, but increases capacitance

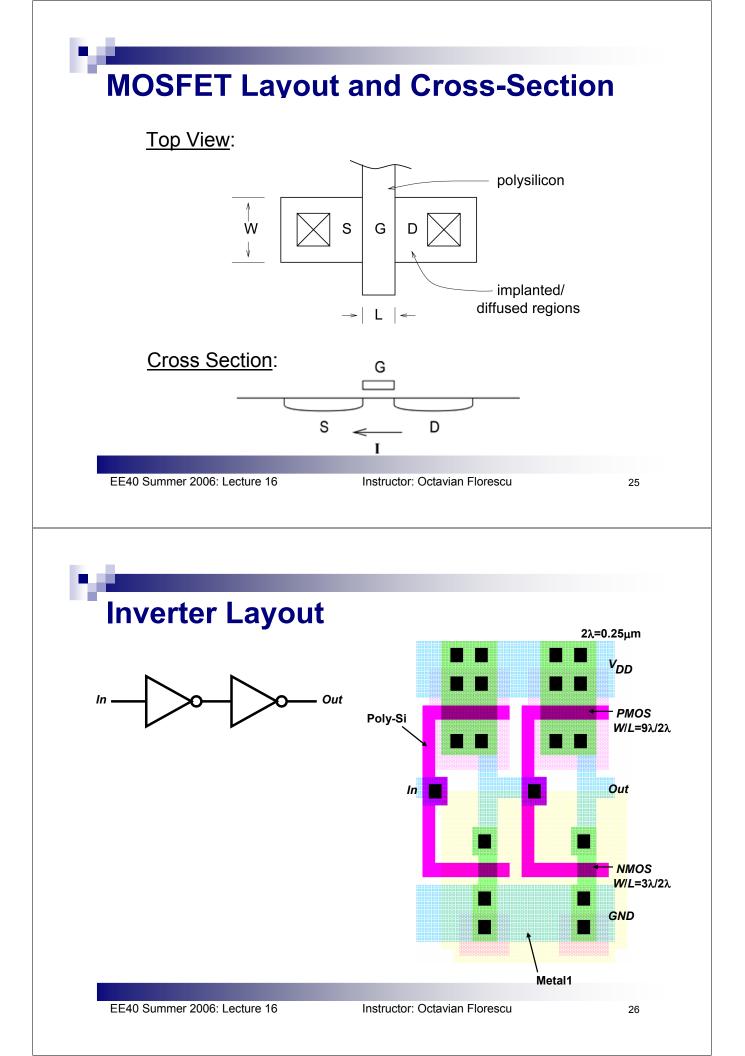

- In order to have the on-state resistance of the PMOS transistor match that of the NMOS transistor (*e.g.* to achieve a symmetric voltage transfer curve), its *W/L* ratio must be larger by a factor of ~3. To achieve minimum propagation delay, however, the optimum factor is ~2.

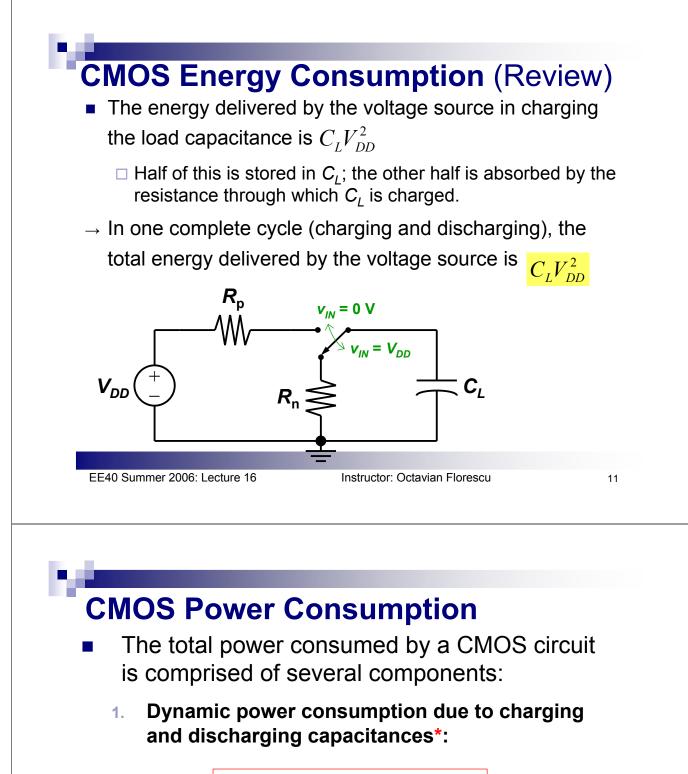

$P_{dyn} = C_L V_{DD}^2 f_{0 \to 1} = C_{EFF} V_{DD}^2 f$

$f_{0 \rightarrow 1}$  = frequency of  $0 \rightarrow 1$  transitions ("switching activity")

*f* = clock rate (maximum possible event rate)

*Effective capacitance* C<sub>EFF</sub> = average capacitance charged every clock cycle

\* This is typically by far the dominant component!

EE40 Summer 2006: Lecture 16

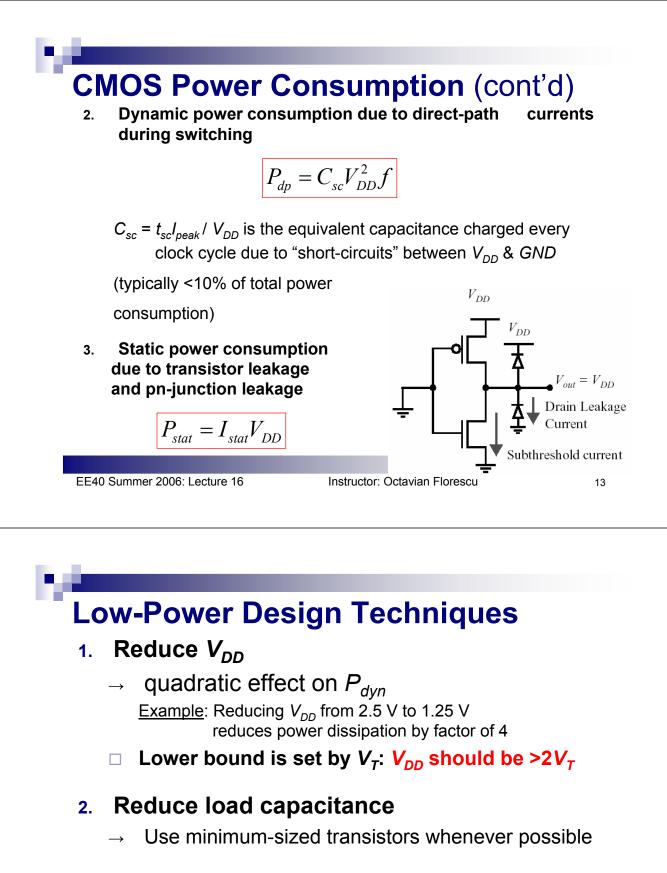

## 3. Reduce the switching activity

involves design considerations at the architecture level (beyond the scope of this class!)